您当前的位置:首页>论文资料>PCI9054在硬件加速卡中的应用

内容简介

数事载术与度用

数事载术与度用PCI9054在硬件加速卡中的应用

赵倩

(国家新闻出版广电总局九五一台河北石家庄050407)

应用研究

摘要:PCI9054是由PLX公司生产的PCI总线接口芯片,广违应用于工业控制及数字信号处理领或本文介绍了PCI9054的基本特性,引脚功能和使用方法,设计了基于PCI9054和数字信号处理芯片TS201的硬件加速处理卡,实境数字广播模拟系统中的信号处理功能详细介绍了数据传输接口和驱动软件的实现方法,通过工程实践证明了PCI9054在PC1总线接口设计中的简便性和实用性。

关键词:PC1总线PCI9054硬件加速DMA

中图分类号:TN919.23

文献标识码:A

文章编号:1007-9416(2015)05-0073-02

Abstract:The PCI9054 is a PCI bus interface chip produced by PLX Technology Inc and is widely used in industrial control and digital signal processing field.This paper introduces the typical features, pin finction and using method of PCI9054, designs a hardware acceleration board based on PCI 9054 and ADSP TS201, which realizes the signal processing fimction in digital radio simulation system. The implementation of data transfer interface and driver sofrware is presented in detail. The convenience and practicability of PCI9054 in the PCI bus interface design are proven through the engine

ering practice

Key Words:PCI bus PCI 9054 hardware acceleration DMA

1引言

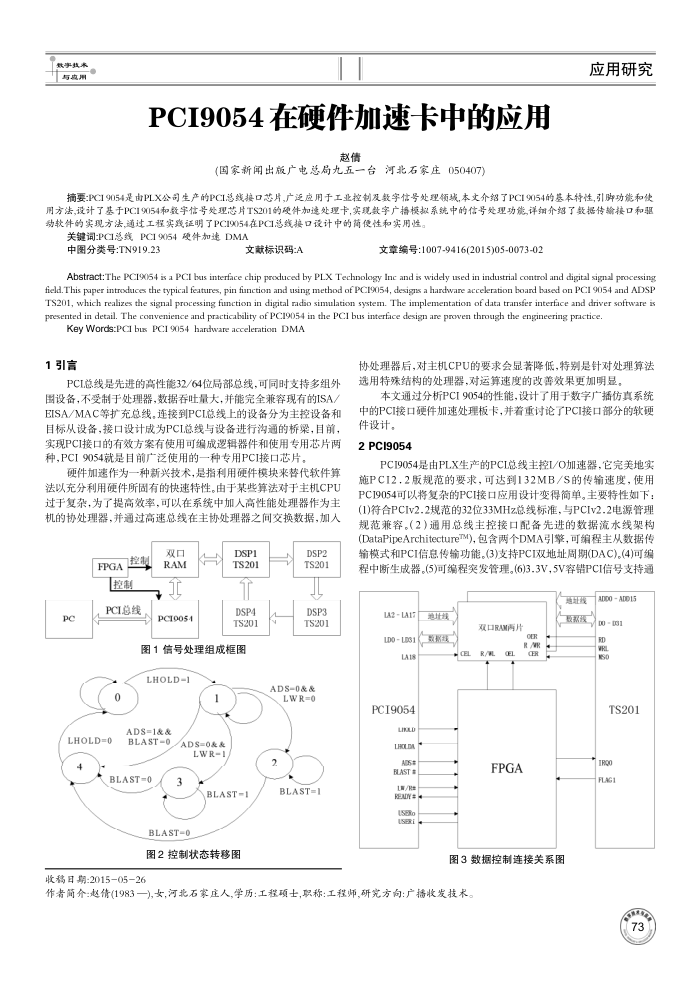

PCL总线是先进的高性能32/64位局部总线,可同时支持多组外图设备,不受制于处理器,数据吞吐量大,并能完全兼容现有的ISA/ EISA/MAC等扩充总线,连接到PCI总线上的设备分为主控设备和目标从设备,接口设计成为PCI总线与设备进行沟通的桥梁,目前,实现PCI接口的有效方案有使用可编成逻辑器件和使用专用芯片两种,PCI9054就是目前广泛使用的一种专用PCI接口芯片。

硬件加速作为一种新兴技术,是指利用硬件模块来禁代软件算法以充分利用硬件所固有的快速特性。由于某些算法对于主机CPU 过于复杂,为了提高效率,可以在系统中加人高性能处理器作为主机的协处理器,并通过高速总线在主协处理器之间交换数据,加人

FPGA控制控制

PCI总线

PC

双口 RAM

PCI9054

DSP1 TS201

t DSP4 TS201

图1信号处理组成框图 LHOLD1

LHOLD=0

ADS=1&&

BLAST=0

BLAST=0

ADS=0&&

LWR-1

BLAST

BLAST=0

图2控制状态转移图

收稿日期:201505-26

DSP2 TS201

DSP3 TS201

ADS=0&& LWR=0

BLAST=1

协处理器后,对主机CPU的要求会显著降低,特别是针对处理算法选用特殊结构的处理器,对运算速度的改善效果更加明显

本文通过分析PCI9054的性能,设计了用于数字广插仿真系统中的PCI接口硬件加速处理板卡,并着重讨论了PCI接口部分的软硬件设计。

2PCI9054

PCI9054是由PLX生产的PCL总线主控I/O加速器,它完美地实施PCI2.2版规范的要求,可达到132MBS的传输速度,使用 PCI9054可以将复杂的PCI接口应用设计变得简单。主要特性如下:(1)符合PCIv2.2规范的32位33MHz总线标准,与PCIv2.2电源管理规范兼容。(2)通用总线主控接口配备先进的数据流水线架构(DataPipeArchitectureTM),包含两个DMA引擎,可编程主从数据传输模式和PCI信息传输功能。(3)支持PCI双地址周期(DAC)。(4)可编程中断生成器。(5)可编程突发管理。(6)3.3V,5V容错PCI信号支持通

施址线

2-LA17地线

数摄线

LDO-LOS1

LA18

PCI9054

LIML LHOLDA A05# BUAST S LW/Re READY tSEko USERi

双口RAM两片

OER

R/N

E FPGA

CER

数然线

ADDO - ADD15

00 - [31 RD

TS201

IRO FLAG1

图3数据控制连接关系图

作者简介赵情(1983一),女,河北石家庄人,学历:工程硕士,职称:工程师,研究方向:广播收发技术。

上一章:PTN绑定错误造成业务中断的故障处理

下一章:UFO 报表二次开发功能