您当前的位置:首页>论文资料>基于FPGA的任意比例图像缩放算法

内容简介

算法分析

算法分析基于FPGA的任意比例图像缩放算法

刘强,晋兆虎

(1.浙江宇视科技有限公司浙江杭州310053;2.华为通信技术有限公司杭州研究所浙江杭州310053)

放事费

摘要:在实际图绿处理系统中,由于系统对实时的要求非常高,所以常采用FPGA进行图像的编放,以利用其强大的并行处理能力。本文提出一种基于FPGA的算法,能够实现复杂的比例缩放,而且结构简单,非常适合工程化。

关键词:图像缩小图像放大FPGA

文献标识码:A

中图分类号:TP391.41

文章编号:1007-9416(2011)12-0126-02

Abstract: Because the demand of the realtime image processing performace is very huge,FPGAbased scaler is adapt to it with the parallel processing capality. The paper presents a simplifiedstructure image pretreatment based on FPGA.It can impliment more complicated image contraciton and amplification algorithm.

Keywords:Image contraction Image amplification FPGA

1、引言

数字图像的缩放在实际生活中被广泛的使用,比如同一DVD 视频源在不同的电视机,计算机上显示的时候,由于不同的显示终端的分辨率不同,而数据源的分辨率是相同的,这样就需要将此视频源进行缩放处理。在一些实时性要求很高的场合,比如视频会议系统、视监控系统等,由于用户需要实时观看到不同视频源的不同分辨率的图像,最常见的应用是监控系统中,监控者可能需要特感兴趣的实时图像进行放大,以便获取更多的监控信息,在这些应用中,对缩放算法的效果和实时特性要求都比较高,FPGA常被用于这类系统的解决方案之中

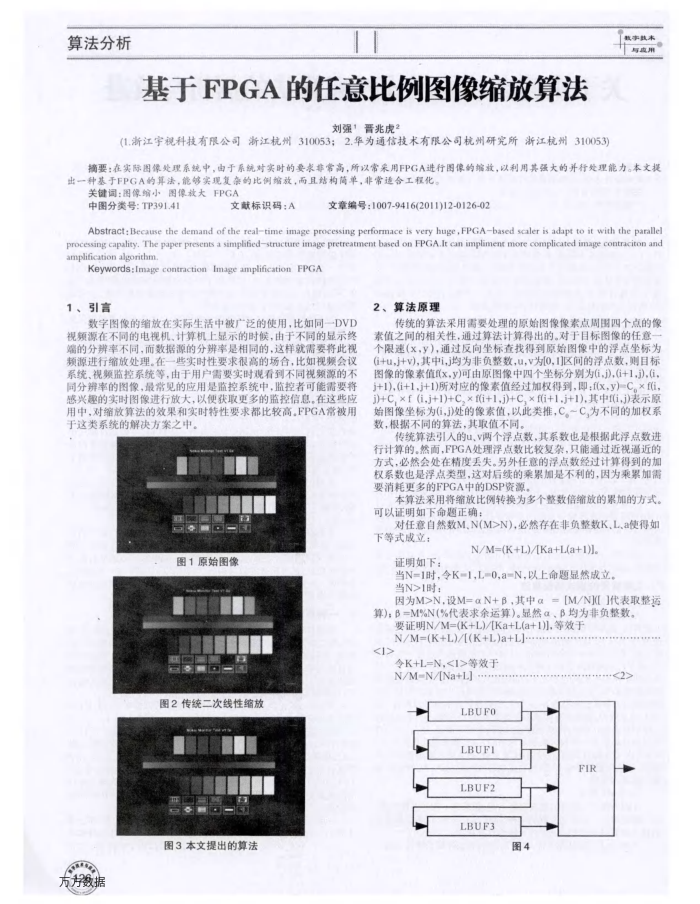

图1原始图像

图2传统二次线性缩放图3本文提出的算法

产数据

2、算法原理

传统的算法采用需要处理的原始图像像素点周围四个点的像素值之间的相关性,通过算法计算得出的。对于目标图像的任意一个限速(x,y),通过反向坐标查找得到原始图像中的浮点垒标为(+u,+v),其中,均为非负整数,u,v为0,1区间的浮点数,则目标图像的像素值(x,y)可由原图像中四个坐标分别为(i.j),(i+1,3).(i, i+1),(i+1.j+1)所对应的像素值经过加权得到.即:f(x,y)=Cxf(i j)+C,×f (i,j+1)+C,×f(i+1,j)+C,×f(i+1.j+1),其中f(i,j)表示原始图像垒标为(i,j)处的像素值,以此类推,CC,为不同的加权系数,根据不同的算法,其取值不同。

传统算法引人的u,v两个浮点数,其系数也是根据此浮点数进行计算的。然面,FPGA处理浮点数比较复杂,只能通过近视通近的方式,必然会处在精度丢失。另外任意的浮点数经过计算得到的加权系数也是浮点类型,这对后续的乘累加是不利的,因为乘累加需要消耗更多的FPGA中的DSP资源,

本算法采用将缩放比例转换为多个整数倍缩放的累加的方式。可以证明如下命题正确:

对任意自然数M.N(M>N),必存在非负整数K、L、a使得如

下等式或立:

证明如下:

N/M=(K+L)/[Ka+L(a+1)]。

当N=1时,令K=1,L=0,a=N,以上命题显然成立。当N>1时:

因为M>N,设M=αN+β,其中α=[M/N]I]代表取整运算):β=M%N(%代表求余运算)。显然α、β均为非负整数。

要证明N/M=(K+L)/[Ka+L(a+1)],等效于 N/M=(K+L)/[(K+L)a+L)......

<1>

令K+L=N,等效于 N/M=N/[Na+L]

LBUFO LBUF1

FIR

LBUF2 LBUF3

图4