基于CYCLONE Ⅱ系列可编程逻辑器件的FPGA最小系统设计

内容简介

设计开发

设计开发基于CYCLONE II系列

可编程逻辑器件的FPGA最小系统设计

刘1刘思艳2陈丽薇3

(1.重庆通信学院特种电源实验室重庆400035;

2.78096部队云南昆明650034;3.重庆育才工程咨询监理有限公司重庆400035)

共中书与质用

摘要:本文从硬件和软件方面分别对基于ALTERA公司的CYCLONEII系列FPGA-EP2C5Q208C8的表入式最小系统设计方法进行了论速。该系统具有CPU总线接口、RS-232审口、模数I2C总线等接口,重点介绍了CPU总线接口的软件实见。该系统可以方便的与外部处理器或系统外设实现通信与互联,以组成目前应用非常广泛的核丧入式控制系统。

关键调:嵌入式系统最小系统EP2C5Q208C8RS-23212C

中图分类号:TN791

文献标识码:A

EP2C5Q208C8是CYCLONEII系列中的重要一员,共有4,608 个LEs,片上RAM共计119,808bits,13个18×18硬件乘法器,2个高性能PLL以及多达142个用户自定义IO,资源非常丰富,足够满足大型设计的需要。目前市场上可以看到多种复杂的基于CYCLONEII 系列FPGA的控制平台进行设计,这些产品往往由于功能复杂,价格居高不下,对于一些具体的应用,这些功能往往存在较多的多余模块,对于善通用户来说这类产品往往难以接近I3)

本文提出一种基于ALTERA公司CYCLONEIⅡI系列FPGA--EP2C5Q208C8的嵌人式最小系统的设计方案,经过对完成设计的控制器进行测试,采用此方案设计的FPGA最小系统运行稳定,具有

结构简单,可靠性高,同时易于对系统进行扩展的特性 1嵌入式系统硬件设计

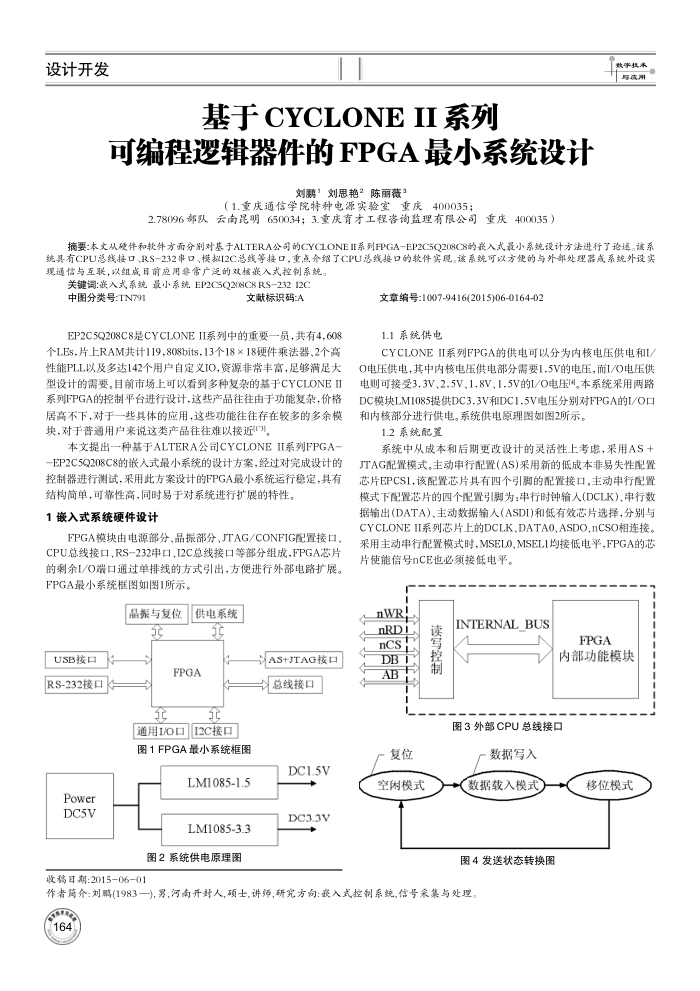

FPGA模块由电源部分,晶振部分,JTAG/CONFIG配置接口、 CPU总线接口、RS-232串口、I2C总线接口等部分组成,FPGA芯片的剩余I/O端口通过单排线的方式引出,方便进行外部电路扩展。 FPGA最小系统框图如图1所示。

晶振与复位

USB接口

RS-232接口 Power DC5V

供电系统

VAS+JTAG按口

FPGA

通用1/0口12C接口图1FPGA最小系统框图

LM1085-1.5 LM1085-3.3

图2系统供电原理图

收稿日期:2015-0601

总线接口

DC1.5V DC3.3V

文章编号:1007-9416(2015)06-0164-02 1.1系统供电

CYCLONEIⅡI系列FPGA的供电可以分为内核电压供电和I/ O电压供电,其中内核电压供电部分需要1.5V的电压,而L/O电压供电则可接受3.3V.2.5V.1.8V,1.5V的L/O电压。本系统采用两路 DC模块LM1085提供DC3.3V和DC1.5V电压分别对FPGA的L/O口和内核部分进行供电。系统供电原理图如图2所示。

1.2系统配置

系统中从成本和后期更改设计的灵活性上考虑,采用AS+

TAG配置模式。主动串行配置(AS)采用新的低成本非易失性配置芯片EPCS1.该配置芯片具有四个引脚的配置接口,主动串行配置模式下配置芯片的四个配置引脚为:串行时钟输人(DCLK)、串行数据输出(DATA)、主动数据输入(ASDI)和低有效芯片选择,分别与 CYCLONEII系列芯片上的DCLK,DATAO,ASDO,nCSO相连接。采用主动串行配置模式时,MSELO,MSEL1均接低电平,FPGA的芯片使能信号nCE也必须接低电平。

nWR! nRDi ncs DB AB

复位空闲模式

读写控制

INTERNAL BUS

FPGA

内部功能模块

图3外部CPU总线接口

数据写入

(数据载入模式图4发送状态转换图

作者简介:刘鹏(1983一),男,河南开对人,硕士,讲师,研究方向:嵌入式控制系统,信号采集与处理。 164

移位模式

上一章:基于FPGA的任意比例图像缩放算法

下一章:基于FPGA千兆以太网数据传输系统设计