您当前的位置:首页>论文资料>基于FPGA的图像采集及压缩系统设计

内容简介

数事载本与度用

数事载本与度用设计开发

基于FPGA的图像采集及压缩系统设计

韩衡畴

(广东农工商职业技术学院机电系广东广州510507)

摘要:介留了一种基于FPGA的图像处理系统设计,该系统主要由视频图像采集和图像压缩两部分组成,实境了对网络图像进行采集和压结的功能。本文采用自项向下的设计方法完成了整个FPGA的逻辑设计,为了简化系统,采用了AItera公司提供的IP款核。完或系统整体设计后,对各模块功能及系统整体遗行验证,分析了各模块的逻辑功能合理性和系统整体的时序正确性。

关键词:FPGA图像采集图像压增网络传输

中图分类号:TP274

文献标识码:A

文章编号:1007-9416(2016)06-0165-02

随着人们对安全的需求日益强烈,视频监控系统作为一种安全防范的手段,越来越受到广泛乏的关注。在视频监控系统中,视频图像的采集、压缩机传输质量直接影响系统的监控质量,因而,高保真准动态图像的采集、压缩和远程传输技术成为许多先进国家计算机领域的重要研究课题,研究网络图像采集及压缩处理技术具有重大的现实意义。由于FPGA在流水线并行处理数据上具有强大优势,具有集成度高,体积小,可灵活配置等优点,在图像处理领域得到广泛应用。本文介绍一种基于FPGA实现图像采集及压缩的设计方案、以便

于图像的网络传输。 1系统总体设计

本文设计了一种能实现对图像进行实时采集和实时压缩的图像采集与压缩系统,系统的总体框图如图1所示。该系统主要包括视频图像采集模块、图像压缩模块,逻辑控制模块和网络传输模块。其中,图像的采集由图像采集模块完成,该模块将CCD报像头输人的 PAL制式模拟视频图像转换为标准的ITU-RBT.656YCbCr4: 2:2格式的8比特视频数据进行输出,采集到的图像经过A/D转换成数字信号后需要进行压缩从而进行网络传输,图像的压缩由图像压缩模块按JPEG标准完成压缩,FPGA逻辑控制模块负责各个芯片之间的时序匹配、发生以及各芯片工作模式和某些工作参数的初始化配置,同时还协调网络传输接口的数据读写,数据传输模块负责将压缩后的图像数据通过网络接口传送到PC,

广”提技物, as 口模状金 25%品折 FEAS

3937R93

60m晶州

头西保黑果换

JPEG信百缩提地

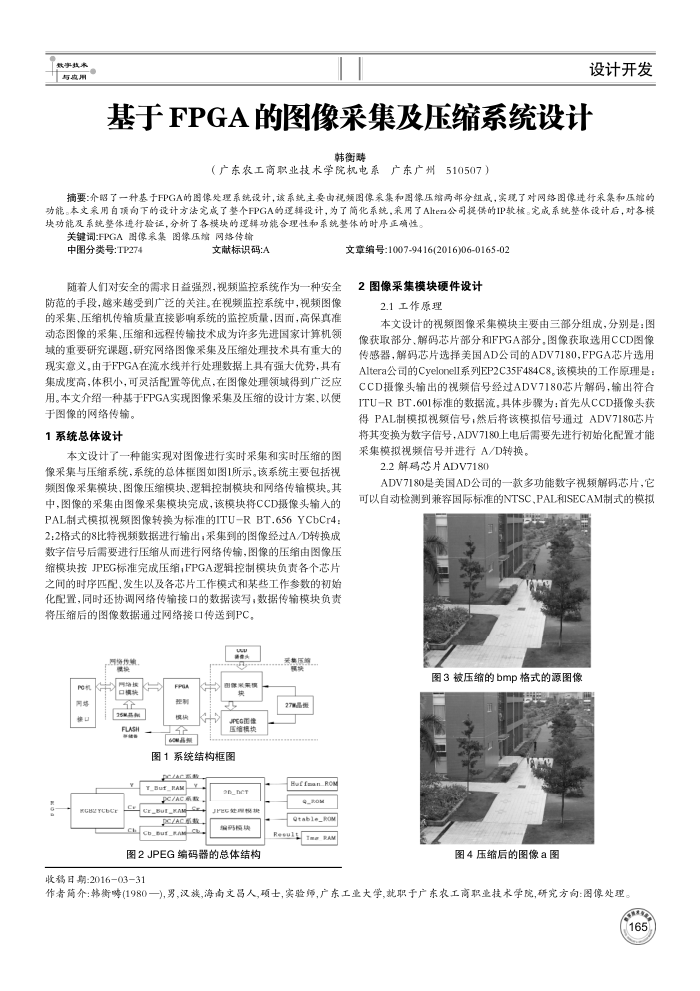

图1系统结构框图 But_rAar

C/ACSR

PE处理桃

PC/AC

nbuf

a

编码模块

图2JPEG编码器的总体结构

收稿日期:2016-03-31

送热区编究

晶

But fuan_ROM g_8.0n 0table_ROM

FeeulLTme RAM

2图像采集模块硬件设计

2.1工作原理

本文设计的视频图像采集模块主要由三部分组成,分别是:图像获取部分、解码芯片部分和FPGA部分图像获取选用CCD图像传感器,解码芯片选择美国AD公司的ADV7180,FPGA芯片选用 AItera公司的Cyelonell系列EP2C35F484C8。该模块的工作原理是: CCD摄像头输出的视频信号经过ADV7180芯片解码,输出符合 ITU-RBT.601标准的数据流,其体步骤为:首先从CCD摄像头获得PAL制模拟视频信号:然后将该模拟信号通过ADV7180芯片将其变换为数字信号,ADV7180上电后需要先进行初始化配置才能采集模拟视频信号并进行A/D转换。

2.2解.爵芯片ADV7180

ADV7180是美国AD公司的一款多功能数字视频解码芯片,它可以自动检测到兼容国际标准的NTSC,PAL和SECAM制式的模拟

图3被压缩的bmp格式的源图像

图4压缩后的图像a图

作者篇介:韩衡畴(1980一),男,汉族,海南文昌人,颈士,实验师,广东工业大学,就职于广东农工商职业技术学院,研究方向:图像处理

165