基于FPGA的PCI Express 3.0高速DMA控制器设计

内容简介

数事载本与度用

数事载本与度用基于FPGA的PCI

Express3.0高速DMA控制器设计

业青青刁节涛李楠孙兆林

(国防科学技术大学电子科学与工程学院湖南长沙410073)

数控技术

摘要:PCIExpress3.0是最新的高造数据传输协议。本文介绍了基于FPGA的PCIExpres3.0的高速传输系统的DMA控制器结构,并详细说明了DMA 控制器的逻辑设计。DMA控制器基于Xilinx公司的Vintex-7FPGAGen3 Integrated BlockfiorPCIExpns硬核开发,对装成标准FIFO结构,达样可以方便地连按采集数据源和四放日标系统。为了验证设计的功能及可靠性,本文搭建了基于PCIExpress3.0x8通道的高速采集图放验证系统。实验表明,DMA控制器达到设计指标。当DMA传输大小为16MB时,8通道的DMA读/写速度均能达到4900MBytes/s,可满足大部分超高速数据采集四放系统传输的需要。

关键词:PCIExpres3.0高违采集四放DMA;FPGAXILINX数据传输

文章编号:1007-9416(2015)08-0003-05

中图分类号:TP39

文献标识码:A

Abstract:This paper introduces a new structure of DMA controller based on FPGA high speed transmission system with PCI Express 3.0, explains the logical design of DMA controller in detail and packages it into a standard FIFO stnicture, which can conveniently adopt to data acquisition or playback system. In order to verify the finction and reliability of the design, a highspeed data acquisition and playback system based on PCI Express 3.0 X8 channel is built. The experiments show that the performance of the system has achieved the design specifications. The read/write speed of PCI Express 3.0 X8 channel DMA controller can reach 4,900MBytes/s when the size of the DMA is 16MB, which can meet the transmission needk of most of the highspeed data acquisition and playback systems.

Key Words:PCI Expres 3.0; High speed acquisition and playback; DMA; FPGA, XILINX, data transmision

1引言

随着海量数据传输存储系统的应用越来越广泛,对传输总线带宽的要求越来越高。高速申行总线以其优越的性能在数据传输系统中得到了广泛的应用,这当中最具代表性的莫过于PCIExpress总线。同时,伴随着FPGA技术的大规模的应用,越来越多的大型系统采用PCIExress总线连接FPGA处理板和PC以实现数据的交互。尽管很多FPGA公司推出了基于PCIExpress协议相关的IP硬核,但是掌握这毕硬核的使用需要对PCIExDress协议具有一定的了解,而且直接使用硬核,带宽很小,开发难度大,移植性差等缺点这些都是造成目前PCIExpress接口设计的瓶颈。为了降低开发难度提高带宽和移植性,许多现有的方案是在PCIExpress硬核中加入高速DMA控制器单元,以此来达到设计需求。

本文提出了一种基于XilinxFPGA的PCIExpress3.0接口

Transaction DataiLink Physical p-qns eor607 Clectrical Gub-blkc

RX

Transaction Data Link Physical Logical Sub-block Clectrical Gub-block RX

图2.1PCIExpress总线的层次结构

收移日期:201507-14

的新型DMA控制器架构,以提高数据传输效率,通道带宽,灵活性和可靠性,硬件方面,我们基于

Xilinx公司的FPGA芯片

XC7VX690T2FFG1761C,实现了PCIExpress3.0的硬件接口,软件方面,基于Windows驱动内核,设计了支持scatter/gather、 MSI中断等机制的上位机驱动。整个系统参照PCIExpress3.0协议规范,最终实现了以DMA方式进行高速数据传输的验证平台,实

现了数据从板卡到PC端、由PC端到板卡的高速通信。 2PCIExpress总线简介

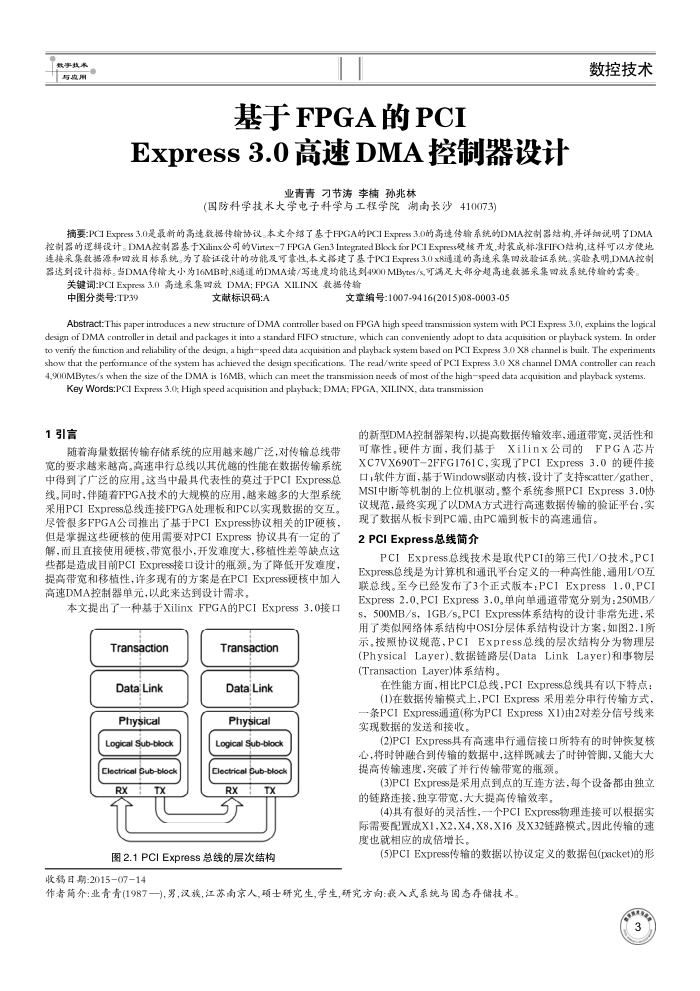

PCIExpress总线技术是取代PCI的第三代I/O技术。PCI Express.总线是为计算机和通讯平台定义的一种高性能,通用L/O互联总线。至今已经发布了3个正式版本:PCIExpress1.0,PCI Express2.0,PCIExpress3.0。单向单通道带宽分别为:250MB/ S,500MB/s,1GB/s,PCIExpress体系结构的设计非常先进,采用了类似网络体系结构中OS1分层体系结构设计方案,如图2.1所示。按照协议规范,PC1Express总线的层次结构分为物理层(Physical Layer)、数据链路层(DataLinkLayer)和事物层(TransactionLayer)体系结构

在性能方面,相比PCI总线,PCIExpress总线具有以下特点:(1)在数据传输模式上,PCI Express采用差分申行传输方式,-条PCIExpress通道(称为PCIExpressX1)由2对差分信号线来实现数据的发送和接收。

(2)PCIExpress具有高速申行通信接口所特有的时钟恢复核心,将时钟融合到传输的数据中,这样既减去了时钟管脚,又能大大提高传输速度,突破了并行传输带宽的瓶颈。

(3)PCIExpress是采用点到点的互连方法,每个设备都由独立的链路连接,独享带宽,大大提高传输效率,

(4)具有很好的灵活性,一个PCIExpress物理连接可以根据实际需要配置成X1,X2,X4,X8X16及X32链路模式。因此传输的速度也就相应的成倍增长。

(5)PCIExpress传输的数据以协议定义的数据包(packet)的形

作者简介:业青青(1987一),男,汉族,江苏南京人,颈士研究生,学生,研究方向:嵌入式系统与固态存储技术。