基于FPGA的图像中值滤波算法硬件系统实现

内容简介

数字技术与应用

数字技术与应用基于FPGA的图像中值滤波算法硬件系统实现

张凌飞

(青海民族大学物理与电子信息工程学院

青海西宁

810007)

应用研究:

摘要:介络一个以XC2S206为核心的视频信号滤波处理累统,该系统为水下图像日标识别和监控提供了一种解决方案,它来用其规算法对图像进行统一,高效的全局变换,滤波增强效率更高,并且采用Xilinx公司的FPGA芯片XC2S200任处理核心,使得该系航结构累赛,配置灵活,使于搏毒。该系统可实时使术下昏暗,模期的视须图像获得较好的味产滤波效采,并输出给液品显示器显示,可应用于水下场景监测成监控,具有很好的市场应周前景。

关键词:FPGA视频信号

味声滤波

中图分类号,TP399

文献标识码:A

视频图像处理的应用越来越广泛,各种图像处理算法日趋成熟热,相关的硬件技术更是不断推陈出新。本文针对FPGA在视频图像处理上的应用,提出了一种基于战波处理的规频系统设计方案,并选用Xilinx 公司的SpartanII系列FPGA芯片XC2S200 为核心,设计实现了系统硬件电路,该硬件平台与相关的算法软件相结合,可实现微光图像增强、视频信号降噪等图像处理。

1XilinxXC2S2001

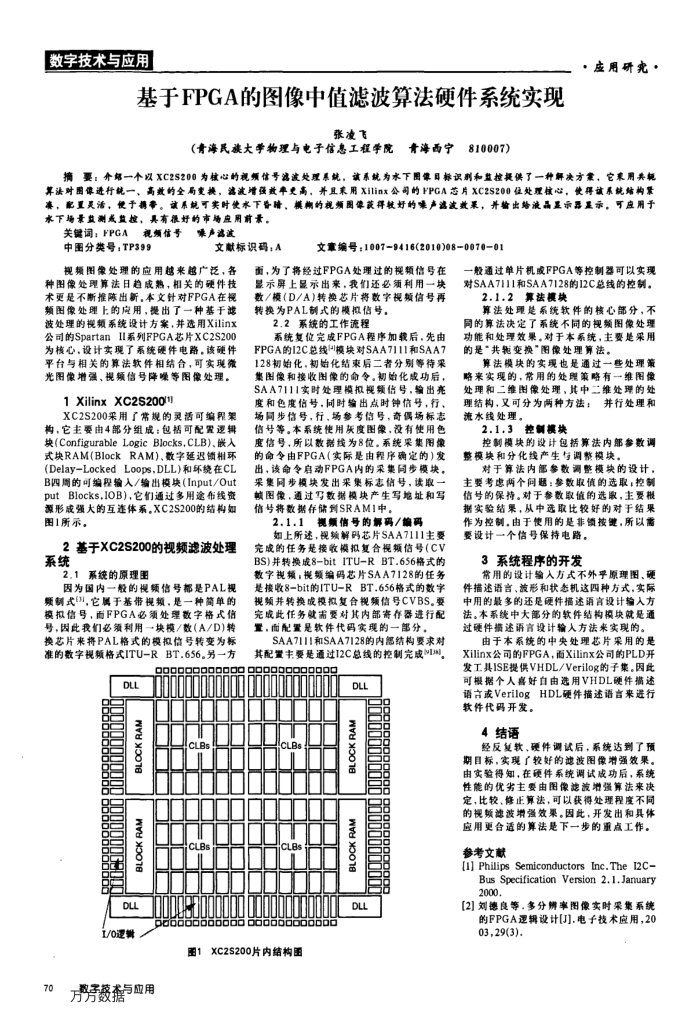

XC2S200采用了常规的灵活可编程架构,它主要由4部分组成:包括可配置逐辑块(Configurable Logic Blocks,CLB),嵌人式块RAM(BlockRAM),数字延迟锁相环(Delay-Locked Loops,DLL)和环绕在CL B四周的可编程输入/输出模块(Input/Out putBlocks,IOB),它们通过多用途布线资源形成强大的互连体系。XC2S200的结构如图1所示。

2基于XC2S200的视频滤波处理系统

2.1系统的原理围

因为国内一般的视频信号都是PAL视频制式3,它属于基带视频,是一种简单的模拟信号,而FPGA必须处理数字格式信号,因此我们必领利用一块模/数(A/D)转换芯片来将PAL格式的模拟信号转变为标准的数字视频格式ITU-RBT.656。另一方

DLL

88888888 6888888

BLOCKRAM 88888888 BLOCKRAM

DLL L/O透载

70

文章编号:1007-9416(2010)08-0070-01

面,为了将经过FPGA处理过的规频信号在显示屏上显示出来,我们还必须利用一块数/模(D/A)转换芯片将数字视频信号再转换为PAL制式的模拟信号,

2.2系统的工作流程

系统复位完成FPGA程序加较后,先由 FPGA的I2C总线模块对SAA7111和SAA7 128初始化,初始化结束后二者分别等待采集图像和接收图像的命令。初始化成功后, SAA7111实时处理模拟规频信号,输出亮度和色度信号,间时输出点时钟信号,行、场同步信号,行,场参考信号,奇偶场标志信号等。本系统使用灰度图像,没有使用色度信号,所以数据线为8位。系统采集图像的命令由FPGA(实际是由程序确定的)发出,该命令启动FPGA内的采集同步模块,采集同步模块发出采集标志信号,读取一赖图像,通过写数据模块产生写地址和写信号将数据存储到SRAM1中,

视频信号的解码/愉码

2.1.1

如上所述,视频解码芯片SAA7111主要完成的任务是接收模拟复合视频信号(CV BS)并转换成8-bitITU-RBT.656格式的数字视频,规频编码芯片SAA7128的任务是接收8-bit的ITU-RBT.656格式的数字视频并转换成模拟复合视频信号CVBS。要完成此任务就需要对其内部寄存器进行配置,而配置是软件代码实现的一部分。

SAA7111和SAA7128的内部结构要求对其配置主要是通过T2C总线的控制完成>I川。

888888888888

3 888888888888

DLL 888888

CLB CLBs

CLBs CLBs

66o6oo68o8o68o68ooooooo

XC2S200片内结构围函1

一数字落在与应用方方数据

BLOCKRAM 3888888888 aoaaaaae BLOCKRAM

DLL

一般通过单片机或FPGA等控制器可以实现对SAA7111和SAA7128的12C总线的控制,

2.1.2算法模块

算法处理是系统软件的核心部分,不同的算法决定了系统不同的视频图像处理功能和处理效果。对于本系统,主要是采用的是“共变换"图像处理算法。

算法模块的实现也是通过一些处理策略来实现的,常用的处理策略有一维图像处理和二维图像处理,其中二维处理的处理结构,又可分为两种方法:并行处理和流水线处理。

2.1.3控制模块

控制模块的设计包括算法内部参数调整模块和分化线产生与调繁模块。

对于算法内部参数调整模块的设计,主要考虑两个间题:参数取值的选取,控制信号的保持。对于参数取值的选取,主要根据实验结果,从中选取比较好的对于结果作为控制。由于使用的是非锁按键,所以需

要设计一个信号保持电路。 3系统程序的开发

常用的设计验人方式不外乎原理图、硬件描述语言、波形和状态机这四种方式,实际中用的最多的还是硬件描述语言设计输人方法。本系统中大部分的软件结构模块就是通过硬件措述语言设计输人方法来实现的。

由于本系统的中央处理芯片采用的是 Xilinx公司的FPGA,面Xilinx公司的PLD开发工具ISE提供VHDL/Verilog的子集。因此可根据个人喜好白由选用VHDL硬件描速语方或VerilogHDL硬件描速语言来进行软件代码开发。

4结语

经反复软,硬件调试后,系统达到了预期目标,实现了较好的滤波图像增强效果。由实验得知,在硬件系统调试成功后,系统性能的优劣主要由图像滤波增强算法来决定,比较、修正算法,可以获得处理程度不同的视频滤波增强效果。因此,开发出和具体应用更合适的算法是下一步的重点工作。

参考文献

[1] Philips Semiconductors Inc. The I2C-

Bus Specification Version 2.1.January 2000.

[2]刘德良等.多分辨率图像实时采集系统

的FPGA逻辑设计[J].电子技术应用,20 03,29(3).