您当前的位置:首页>论文资料>基于FPGA的信号发生器

内容简介

应用研究

应用研究基于FPGA的信号发生器

李君华

(91245部队45分队辽宁葫芦岛125000)

数字投本开写流用

摘要:信号发生器在工业测试领或有达非常广泛的应用,传统的信号发生器存在频率不高,稳定性较差等问题。本文使用FPGA实现了产生可控频率的正弦波方波的信号发生器。通过改变时钟可实现对波形频率的择,通过ROM表实现多种波形的存储,给出了DA转换交放电路Verilng程序,实验仿真结果,表明本文提出的方法可行,可操控性强,成本低,编程方便,能够产生较高的频率,稳定性大大加强。

关键调:FPGAVerilog信号发生器

中图分类号:TM935.2

文献标识码:A

文章编号:1007-9416(2015)01-0078-02

Abstract:The single generator is widely used in industrial testing, while the frequency of traditional signal generator is not high, poor stability problems. This paper used FPGA to realize the single generator to generate controllable frequency sine and square wave. By changing the clock single can be realized on the waveform or frequency choice. Through the realization of a variety of waveforms R OM table storage, the DA conversion circuit and verilog language program are given. Experimental results show that the method proposed in this paper is feasible,strong operability,low cost,programming convenience, can produce higher frequencies, greatly enhanced stability.

Key Words:FPGA Verilog the signal generator

在工业应用中,会用到高频正弦信号,为解决这一间题通常情况下,会使用函数发生器。可在某些场所,函数发生器体积较大,重量中,集成度差。面使用FPGA实现DDS,则可使设备小型化、轻量化",通过改变ROM表和读取ROM表的速率可以调整所需波形的相位、频率、幅度,集成度更高,在一片FPGA上实现其他功能的同时具有多个DDS芯片的功能。

本文使用FPGA设计产生的DDS,可以输出多种频率的正弦波,方波-4使用Verilog语言编写程序,结构简单,可以根据需要调整 ROM表中的值实现多种波形的选取,可以通过控制读取ROM表的速度产生所需波形的额率。在不更改硬件电路的基础上实现多多种

频率波形的检测,所以可靠性高,方便快捷。 1原理设计

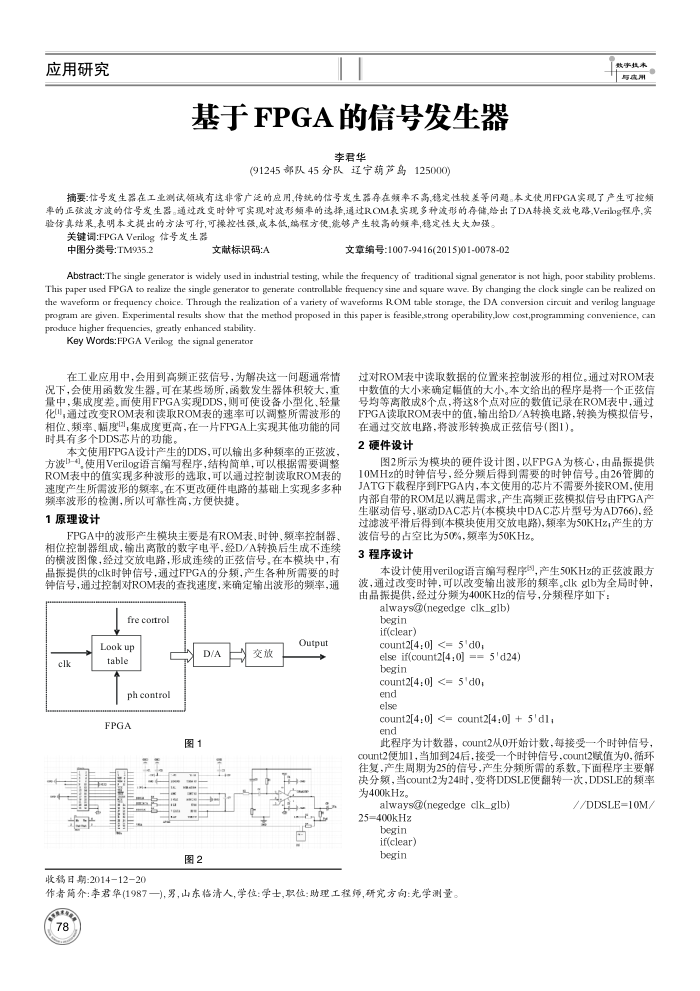

FPGA中的波形产生模块主要是有ROM表、时钟频率控制器、相位控制器组成,输出离散的数字电平,经D/A转换后生成不连续的横波图像,经过交放电路,形成连续的正弦信号,在本模块中,有品振提供的clk时钟信号,通过FPGA的分频,产生各种所需要的时钟信号,通过控制对ROM表的查找速度,来确定输出波形的频率,通

frecortrol

Look up

elk

H

table

ph control FPGA

收稿日期:2014-12-20

D/A

图1 图2

交放

Output

过对ROM表中读取数据的位置来控制波形的相位,通过对ROM表中数值的大小来确定幅值的大小。本文给出的程序是将一个正弦信号均等离散成8个点,将这8个点对应的数值记录在ROM表中,通过 FPGA读取ROM表中的值,输出给D/A转换电路,转换为模拟信号,

在通过交放电路,将波形转换成正弦信号(图1) 2硬件设计

图2所示为模块的硬件设计图,以FPGA为核心,由品振提供 10MHz的时钟信号,经分频后得到需要的时钟信号。由26管脚的 JATG下载程序到FPGA内,本文使用的芯片不需要外接ROM,使用内部自带的ROM足以满足需求。产生高频正弦模拟信号由FPGA产生驱动信号,驱动DAC芯片(本模块中DAC芯片型号为AD766),经过滤波平滑后得到(本模块使用交放电路),频率为50KHz;产生的方

波信号的占空比为50%,额率为50KHz。 3程序设计

本设计使用verilog语言编写程序,产生50KHz的正弦波跟方波,通过改变时钟,可以改变输出波形的频率。clkglb为全局时钟,由品报提供,经过分频为400KHz的信号,分频程序如下,

always@(negedge clk_glb)

begin if(clear)

count2[4:0] <= 5'd0;

else if(count2[4:0] == 5'd24) begin

count2[4:0] <= 5'd0,

end else

count2[4: 0] <= count2[4:0] + 5'd], end

此程序为计数器,count2从0开始计数,每接受一个时钟信号, count2便加1,当加到24后,接受一个时钟信号,count2赋值为o,循环往复,产生周期为25的信号,产生分频所需的系数。下面程序主要解决分额,当count2为24时,变将DDSLE便翻转一次,DDSLE的频率

为400kHz。

always@(negedge clk_glb)

25=400kHz begin if(clear) begin

作者篇介:李君华(1987一),,男,山东格清人,学位:学士,职位:助理工程师,研究方向:光学测量。

//DDSLE=10M/