您当前的位置:首页>论文资料>基于FPGA的北斗卫星信号接收机设计

内容简介

设计开发

设计开发基于FPGA的北斗卫星信号接收机设计

刘中华刘文红

(上海电机学院上海200240)

共中书与质用

摘要获得准确可靠的北平卫星信号是卫星信号解算的基础和关键本文设计了以FPGA为核心的软硬件相结合的丧入式系统通过天线和模拟电露接收、放大原始卫星信号并进行滤波,通过FPGA控制本振与原始卫量信号赢频并送入高速AD,最后通过FPGA控制USB接口将原始信号发送到电脑主机以便进行后续信号解算研究。

关键词:FPGA北平卫量信号USB表入式系统中图分类号:TN927

文献标识码:A

1引言

目前,全球卫星定位系统主要有四种:美国的GPS、俄罗斯的 GLONASS,欧盟的伽利略卫星导航系统和中国自主研发的北斗卫星导航系统。由于卫星导航系统可以全天候实时给出载体具体资态和位置信息,在民用和军用领域都有重要的战略意义。相对于GPS,北斗导航系统的相应研发和应用产业链还不完善,由于条件限制,目前对北斗导航系统的研究多集中于对完成捕获和跟踪后的卫星信号进行处理,而对北斗卫星信号捕获和跟踪算法的研究由于较难获得准确的原始北斗卫星信号而难以进行。

为获得准确的原始北斗卫星信号,受参考文献[11-[3的启发,本文设计了以FPGA为核心的软硬件相结合的嵌入式系统,通过北斗频段接收天线和模拟电路接收、放大和滤波接收到的卫星信号,然后通过FPGA控制本振与卫星信号混频并送人高速AD,最后通过 FPGA控制680I3芯片将AD转换的原始卫星信号通过USB发送到上位机。本文同时使用VC6开发环境设计了接收端的接收程序,将接收的结果转换成文本文件。最后,本文在Matlab编译环境下,运行预先设计好的信号捕获和跟踪算法,验证了本文所设计的卫星信号接收机的功能和性能。

2卫星信号接收机设计

北斗目前有北斗一代和北斗二代,每代信号的额点不同,且代

天线

MMIC低噪声放大器声表带通滤波器

高连AD

FPGA ( altera ep 2c70) + CPLD

文章编号:1007-9416(2014)07-0144-02

内也有若干频点,虽然硬件处理上需要配置的电路参数不同,但设计原理相同。本文选取北斗二代B1频点作为设计目标,即接收电路以1561.098MHz为中心频率。

2.1总体设计

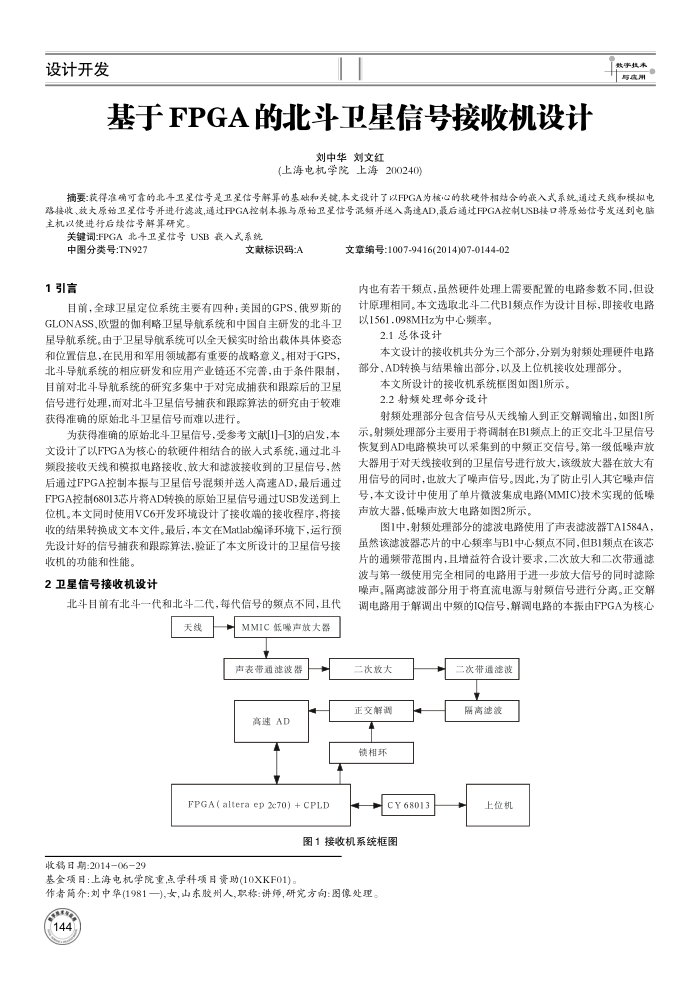

本文设计的接收机共分为三个部分,分别为射频处理硬件电路部分、AD转换与结果输出部分,以及上位机接收处理部分。

本文所设计的接收机系统框图如图1所示。 2.2射频处理部分设计

射频处理部分包含信号从天线输人到正交解调输出,如图1所示。射频处理部分主要用于将调制在B1频点上的正交北斗卫星信号恢复到AD电路模块可以采集到的中频正交信号。第一级低噪声放大器用于对天线接收到的卫星信号进行放大,该级放大器在放大有用信号的同时,也放大了噪声信号。因此,为了防止引人其它噪声信号,本文设计中使用了单片微波集成电路(MMIC)技术实现的低噪声放大器,低噪声放大电路如2所示。

图1中,射频处理部分的滤波电路使用了声表滤波器TA1584A,虽该滤波器芯片的中心频率与B1中心频点不同,但B1频点在该芯片的通频带范围内,且增益符合设计要求,二次放大和二次带通滤波与第一级使用完全相同的电路用于进一步放大信号的同时滤除噪声,隔离滤波部分用于将直流电源与射额信号进行分离。正交解调电路用于解调出中频的IQ信号,解调电路的本振由FPGA为核心

二次放大正交解调锁相环

CY68013

图1接收机系统框图

收移日期:2014―0629

基金项目:上海电机学院重点学科项目资助(10XKF01)

作者篇介:刘中华(1981一),女,山东胶州人,职称:讲师,研究方向:图像处理。 4

二次带通滤被隔离泄波

上位机