您当前的位置:首页>论文资料>基于FPGA千兆以太网数据传输系统设计

内容简介

设计开发

设计开发基于FPGA千兆以太网数据传输系统设计

王媛丽

(长春理工大学吉林长130000)

共中书与

摘要:日前千兆以太网其有传输距离选、传输速度快、稳定可靠等优点是当前丧入式系统研究的重点。本文道过利用FPGA内部的MAC硬检与 Marvell88E1111物理层芯片相连接,实现千兆以太网数据传输系统。该系统中使用UPP协议和IP协议以及与上位机通信的ARP请求和应签,通过上住机可验证该系统的正确性和可靠性。

关键词:千光以太网FPGAUPP协议MAC慎

中图分类号:TP393.11 1引言

文献标识码:A

以前的以太网通信方案大多数使用DSP器件、ARM器件或单片机,数据最高传输速率最高为10MbDS,远远不能当今所需求的高速、高性能传输速率要求。由于FPGA拥有丰高的逻辑和管脚资源,常用于高速数据处理和通信的最人式系统。通过使用FPGA器件可使得以太网速率可达到1000Mbps,可以直接与网络上的其他终端相连。

本文设计一个以FPGA为核心的嵌人式千兆以太网数据传输系统,为了更好地为上位机软件所支持,通过利用UDP/IP协议来完

成数据到上位机的高速传输。 2系统总体设计

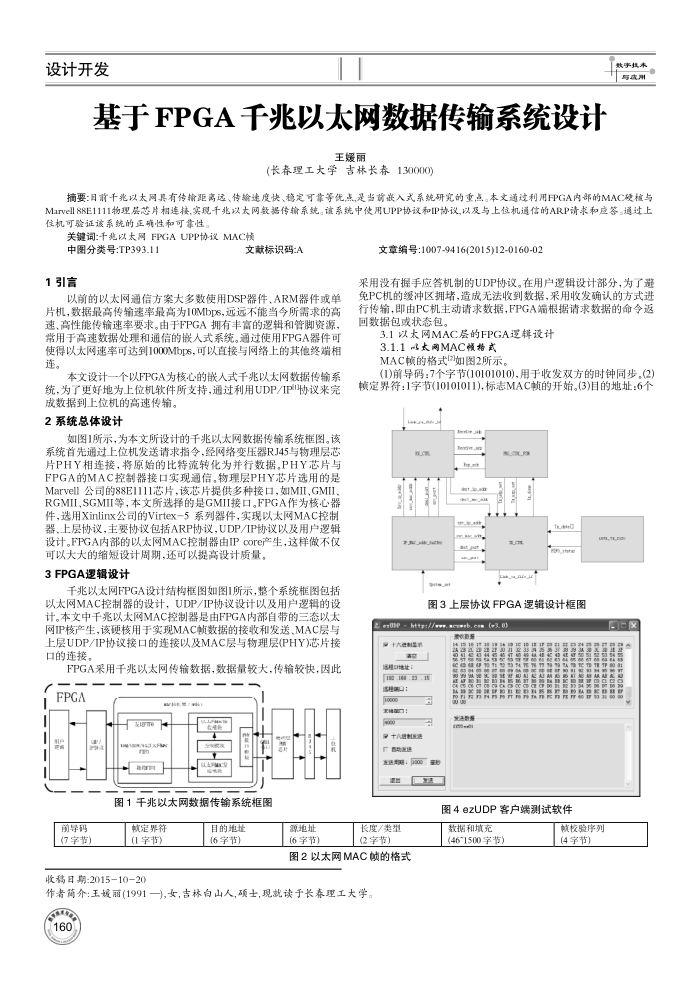

如图1所示,为本文所设计的千兆以太网数据传输系统框图。该系统首先通过上位机发送请求指令,经网络变压器RJ45与物理层芯片PHY相连接,将原始的比特流转化为并行数据。PHY芯片与 FPGA的MAC控制器接口实现通信,物理层PHY芯片选用的是 Marvell公司的88E1111芯片,该芯片提供多种接口,如MII,GMI、 RGMII、SGMII等,本文所选择的是GMII接口。FPGA作为核心器件,选用Xinlinx公司的Virtex-5系列器件,实现以太网MAC控制器、上层协议,主要协议包括ARP协议,UDP/IP协议以及用户逻辑设计。FPGA内部的以太网MAC控制器由IPcore产生,这样做不仅

可以大大的缩短设计周期,还可以提高设计质量。 3FPGA逻辑设计

于兆以太网FPGA设计结构框图如图1所示,整个系统框图包括以太网MAC控制器的设计,UDP/IP协议设计以及用户逻辑的设计。本文中千兆以太网MAC控制器是由FPGA内部自带的三态以太网IP核产生,该硬核用于实现MAC数据的接收和发送、MAC层与上层UDP/IP协议接口的连接以及MAC层与物理层(PHY)芯片接口的连接。

FPGA采用千兆以太网传输数据,数据量较大,传输较快,因此 FPGA

Brpt( ra

KFTe

图1千兆以太网数据传输系统框图

前导码(了字节)

顿定界符(1字节)

收移日期:2015-10-20

目的地址(6字节)

源地址(6字节)

文章编号:1007-9416(2015)12-0160-02

采用没有握手应答机制的UDP协议。在用户逻辑设计部分,为了避免PC机的缓冲区拥堵,造成无法收到数据,采用收发确认的方式进行传输,即由PC机主动请求数据,FPGA端根据请求数据的命令返回数据包或状态包。

3.1以太网MAC层的FPGA逻辑设计

3.1.1以太网MAC格式 MAC赖的格式如图2所示。

(1)前导码:7个字节(10101010),用于收发双方的时钟同步。(2) 慎定界符:1字节(10101011),标志MAC慎的开始。(3)目的地址:6个

,

图3上层协议FPGA逻辑设计框图

IP http://..

十大进制品!

清空总理地址:

[182 .168.23.15

选口: 1000

En

2十A进制通 B

:300

长度/类型(2字节)

图2以太网MAC顿的格式

作者简介:王媛丽(1991一),女,吉林白山人项士,现就读于长泰理工大学 60

蒙更 a究

图4ezUDP客户端测试软件

数据和填充(46"1500字节)

顿校验序列(4字节)