您当前的位置:首页>论文资料>基于FPGA的视频以太网传输

内容简介

通信技术

通信技术基于FPGA的视频以太网传输

李嘉琛杨光

(长券理工大学电子信息工程学院,吉林长春130022)

数事共与或用

摘要:为解决视频传输实时性问题,提出采用现场可竭程门阵列(FPGA)作为主控芯片来控制CMOS传感器进行图像采集,然后和上位机之阔进行以太网数据通信。加入ChipScope软件进行在线逻释分析。实验结果表明系统实现了高质量视频实时传输,且具有耗能低、稳定性高等优点。

关键词:FPGA;图像采集;以太网

中图分类号:TP393.11

文献标识码:A

面对目益增长的数据流和多媒体服务,大容量、高速率,多功能模块高端网络产品的市场规模将不断扩大,以太网的出现能够很好地满足这一市场需求TCP(TransmissionControl Protocol)和UDP(UserDatagramProtocol)属于传输层协议。TCP是基于连接的协议,在正式收发数据前,必须建立可靠的连接,因此可以提供IP环境下数据的可靠传输,但也使得通信效率变低。UDP协议不属于连接型协议,它不与对方建立连接,而是直接就把数据包发送过去。因而具有资源消耗小、在数据传输过程中延迟小和传输效率高等优点,可以有效地实现图像数据快速传输。FPGA在高速数据信号采集、处理具有最为显著优势,且集成度高,功耗低,编程配置灵活。为此本文就FPGA和UDP/IP协议相结合的方式设计了一个视频快速传输

系统,并从时序仿真、功能仿真和硬件平台上验证了其可行性。 1系统概述

为提高系统的集成度、可靠性和稳定性,首先对主控制器进行选择,FPGA打破了顺序执行模式,在每个时钟周期内可完成更多的处理任务,远远超越了数字信号处理器(DSP)的运算能力。本设计中选用Xilinx公司低成本的Spartan6XC6SLX9作为主控芯片,采用 Realtek公司的PHY芯片RTL8211E来实现以太网数据通信。

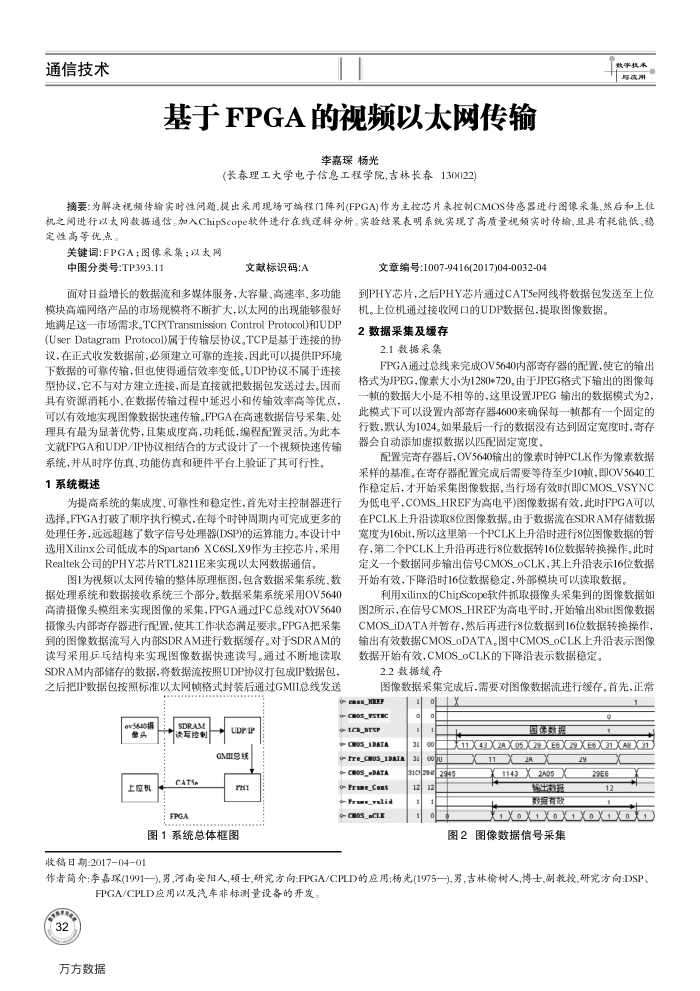

图1为视频以太网传输的整体原理框图,包含数据采集系统、数据处理系统和数据接收系统三个部分。数据采集系统采用OV5640 高清摄像头模组来实现图像的采集,FPGA通过PC总线对OV5640 摄像头内部寄存器进行配置,使其工作状态满足要求。FPGA把采集到的图像数据流写入内部SDRAM进行数据缓存。对于SDRAM的读写采用乒乓结构来实现图像数据快速读写。通过不断地读取 SDRAM内部鳍存的数据,将数据流按照UDP协议打包成IP数据包,之后把IP数据包按照标准以太网顿格式封装后通过GMIL总线发送

文章编号:1007-9416(2017)04-0032-04

到PHY芯片,之后PHY芯片通过CAT5e网线将数据包发送至上位

机。上位机通过接收网口的UDP数据包,提取图像数据。 2数据采集及缓存

2.1数据采集

FPGA通过总线来完成OV5640内部寄存器的配置,使它的输出格式为JPEG,像素大小为1280*720,由于JPEG格式下输出的图像每-慎的数据大小是不相等的,这里设置JPEG输出的数据模式为2,此模式下可以设置内部寄存器4600来确保每一顿都有一个固定的行数,默认为1024。如果最后一行的数据没有达到固定宽度时,寄存器会自动添加虚拟数据以匹配固定宽度。

配置完寄存器后,OV5640输出的像素时钟PCLK作为像素数据采样的基准,在寄存器配置完成后需要等待至少10慎,即OV5640工作稳定后,才开始采集图像数据。当行场有效时(即CMOS_VSYNC 为低电平,COMS_HREF为高电平)图像数据有效,此时FPGA可以在PCLK上升沿读取8位图像数据。由于数据流在SDRAM存储数据宽度为16bit,所以这里第一个PCLK上升沿时进行8位图像数据的暂存,第二个PCLK上升沿再进行8位数据转16位数据转换操作。此时定义一个数据同步输出信号CMOS_oCLK,其上升沿表示16位数据开始有效,下降沿时16位数据稳定,外部模块可以读取数据

利用xilinx的ChipScope软件抓取摄像头采集到的图像数据如图2所示,在信号CMOS_HREF为高电平时,开始输出8bit图像数据 CMOS_iDATA并暂存,然后再进行8位数据到16位数据转换操作,输出有效数据CMOS_oDATA图中CMOS_oCLK上升沿表示图像数据开始有效,CMOS_oCLK的下降沿表示数据稳定。

2.2数据缓存

图像数据采集完成后,需要对图像数据流进行缓存。首先,正常

o- emes_HKEF

ov5640摄 eA

上位机

快写腔

CAT FPGA

LDPIP GM总线

rH

图1系统总体框图

收稿日期:2017-04-01

RASASOND-se-CHOS_iDATA

-Tre_CM05_1DATA

O-CHOS_αDATA Frme_Cent Frme_lid-CHOS_aCLX

31

x

0

国保政据

EEXX SOXEE

00

31029e2945

12

X1143X2A05X

出数摄数据有效

67

29E6 12

GXXXXXXX

图2图像数据信号采集

作者简介:李嘉璨(1991一)男,河南安阳人,项士,研究方向:FPGA/CPLD的应用:杨光(1975一),男.吉林愉树人,博士,副教投,研究方向:DSP

FPGA/CPLD应用以及汽车非标测量设备的开发

万方数据