基于OFDM技术重复结构训练符号的FPGA研究

内容简介

应用研究

应用研究基于OFDM技术

重复结构训练符号的FPGA研究

张恺1李智2

(1.沈阳理工大学辽宁沈阳110159;2.沈阳海关辽宁沈阳110159)

与皮

摘要:本文介绍了一种重复结构训练符号的生成。应用VerilogHDL实现m序列发生器和随机存取存储器等模块来构造所需训练符号,并且使该重复结构训练符号按要求经过IFFT变换实现了正交频分复用,作为已知信息加入待发送OFDM符号,将其置于OFDM符号前或由多个OFDM 并号构成的慎的前部。程序在XilinxISE设计软件中设计并经Modelsim仿真,仿真结果表明,系统工作可靠,满足设计要求。

关键调:OFDM重复结构FPGA

中图分类号:TN919.3

文献标识码:A

1、基于S&C算法(11的训练符号结构

文章编号:1007-9416(2012)09-0048-01

使在计算过程中进行中间数据的缩减。

此算法是由T.Schmidl&D.Cox提出的,算法通过用两个特殊的训练符号实现OFDM系统的时闻同步与频率同步,训练符号1在时域上的前后两部分相同,频域上为偶颊率上传输PN序列,在奇频

率上传输0。训练符号1则满足以下公式:

p(n)= p n+=

(1)

训练符号2是包含两个PN序列,二个是通过奇频率传输,用来进行信道估计,另一个通过偶频率传输,并且与训练符号1上偶频率

传输的PN序列差分关系为C,,用来计算整数赖偏估计。 2、重复结构训练符号的生成及仿真

2.1训练符号1的生成

首先,应用VerilogHDL实现m序列发生器。m序列是最大长度线性反馈移位寄存序列的简称,它作为一种基本的伪随机序列,具有随机性,规律性和良好的自相关性等3)。因此,生成级数n=5,周期D=127的m序列作为训练符号的来源。

如前文所述,训练符号1在时域上的前后两部分相同,因此选取 Ⅱ=7的m序列的128位,训练符号1在频域上为偶赖率上传输PN序列,在奇频率上传输o,应用VerilogHDL实现时可以对m序列的 128位每隔两位插人两个0来实现在奇频率上传输0的要求,为了实现每隔两位插人两个0,原来的审行输入转换为并行的256位,因训练符号1在时域上的前后两部分相同,再将并行的256位复制扩展为 512位的并行输出。对所生成的并行512位符号进行QPSK调制,将调制后的数据符号进行IFFT变换。在这里调用IPCore实现一个256 点,位宽为8bit的IFFT模块。在IPCore设计时,令SCALE_SCH=1, /shiyan0813_tb01/uut/ram_021s/state1s

thoukat

nne/stzn=ueubnn/togsteouekus/

2

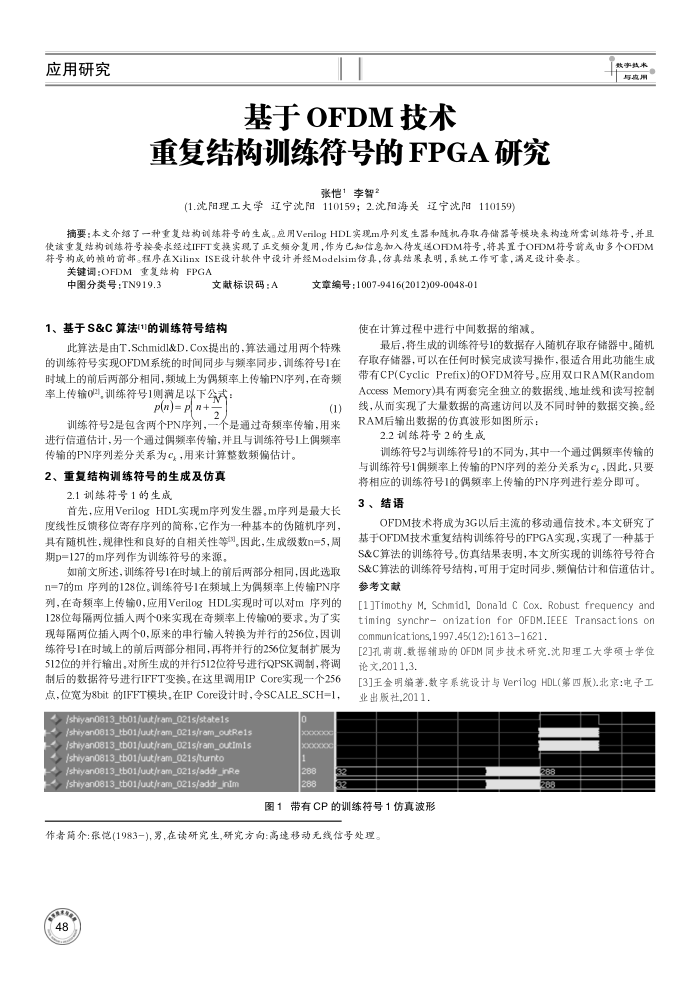

最后,将生成的训练符号1的数据存人随机存取存储器中。随机存取存储器,可以在任何时候完成读写操作,很适合用此功能生成带有CP(Cyclic Prefix)的OFDM符号。应用双口RAM(Random AccessMemory)具有两套完全独立的数据线,地址线和读写控制线,从而实现了大量数据的高递访间以及不同时钟的数据交换。经 RAM后输出数据的仿真波形如图所示:

2.2训练符号2的生成

训练符号2与训练符号1的不同为,其中一个通过偶颠率传输的与训练符号1偶频率上传输的PN序列的差分关系为c,因此,只要将相应的训练符号1的偶颠率上传输的PN序列进行差分即可。 3、结语

OFDM技术将成为3G以后主流的移动通信技术。本文研究了基于OFDM技术重复结构训练符号的FPGA实现,实现了一种基于 S&C算法的训练符号。仿真结果表明,本文所实现的训练符号符合 S&C算法的训练符号结构,可用于定时同步,频偏估计和信道估计。参考文献

[1JTimothy M, Schmid1, Donald C Cox. Robust frequency and timing synchr- onization for OFDM.IEEE Transactions on communications,1997.45(12):16131621

[2]孔前期.数据辅助的OFDM同步技术研究.沈阳理工大学颈士学位论文,2011,3

[3]王金明编著.数字系统设计与Verilog HDL(第四板).北京:电子工业出版社,2011.

288 288

图1带有CP的训练符号1仿真波形

作者简介:张恺(1983-),男,在读研究生,研究方向:高速移动无线信号处理