����ǰ��λ�ã���ҳ>��������>����FPGA�ĵ�ѹ����LC����������о�

����FPGA�ĵ�ѹ����LC����������о�

���ݼ��

Ӧ���о�

Ӧ���о���Ƥ

����FPGA�ĵ�ѹ����LC����������о�

������1������2

��1.���ϻ���ߵ�ר��ѧУ��������ϵ��������453002��2.���ϻ���ְҵѧԺ���ӹ���ϵ����֣��450002��

ժҪ�����������һ�ֻ���FPGA�ĵ�ѹ����LC�����Ƶ�ʿɵ�����LC�������ÿ�ʷ���ֵ�Ķ����ܹ��ɣ������Ƶ�ʺϳ��� MC145152�п��Ƶ�ѹ����FPGA+��Ƭ����Ϊ����ϵͳ�IJ�ز��֣�����Ӳ���������Խ��и�����ģ��ı�̣����Գ�����б�����ܷ��棬��������������֤ϵͳ��Ƶ���ȷ�ԡ�

�ؼ�����VHDLFPGA��ѹ����LC��������

��ͼ����ţ�TN752 1��ϵͳ���Ҫ��

���ױ�ʶ�룺A

���±�ţ�1007-9416(2011)09-0056-02

ѡ�ñ��ݶ����ܲ�����һ��������Ƶ�ѹ���Ϳ�ʵ�ֱ�������Ƶ��

��ƻ���FPGA�ĵ�ѹ����LC�����������Ҫ����"�£�(1) ������������Ҳ����������Ե�ʧ�档��2)���������Ƶ�ʷ�Χ�� 12~30MHz.(3)Ƶ���ȶ������Ҫ����0.001��(4)�����ѹ���ֵ��1V��0.2V(5)�ܹ�ʵ�����Ƶ�ʵIJ�����ͼ����ʾ�������ļ�

��Ϊ100KHz��(6)���Ҫ��Ƶ�ʿ���ʵʱ���������ҿ�����ʾ�� 2��ϵͳ������巽��

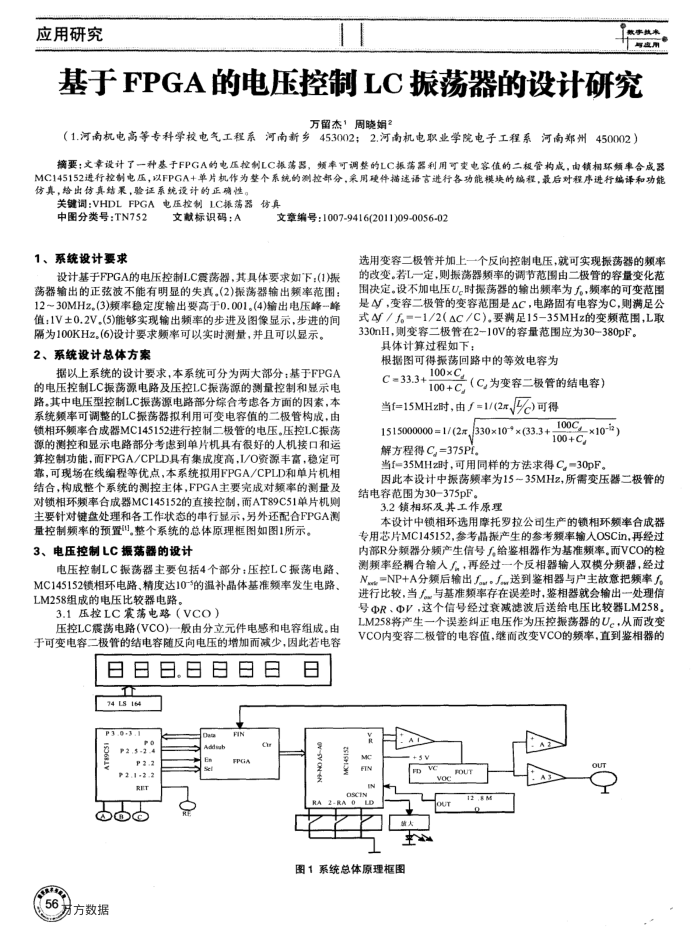

������ϵͳ�����Ҫ��ϵͳ�ɷ�Ϊ���֣�����FPGA �ĵ�ѹ����LC��Դ��·��ѹ��LC��Դ�IJ������ƺ���ʾ��·�����е�ѹ�Ϳ���LC��Դ��·�����ۺϿ��Ǹ��������������ϵͳƵ�ʿɵ�����LC�����������ÿɱ����ֵ�Ķ����ܹ��ɣ������Ƶ�ʺϳ���MC145152���п��ƶ����ܵĵ�ѹ��ѹ��LC��Դ�IJ�غ���ʾ��·���ֿ�������Ƭ�����кܺõ��˻��ӿں�������ƹ��ܣ���FPGA/CPLD���м��ɶȸߣ�I/O��Դ�ḻ���ȶ��ɿ������ֳ����߱�̵��ŵ㣬��ϵͳ����FPGA/CPLD�͵�Ƭ�����ϣ���������ϵͳ�IJ�����壬FPGA��Ҫ��ɶ�Ƶ�ʵIJ����������Ƶ�ʺϳ���MC145152��ֱ�ӿ��ƣ���AT89C51��Ƭ������Ҫ������̴���������״̬�Ĵ�����ʾ��������FPGA��

������Ƶ�ʵ�Ԥ�ã�������ϵͳ������ԭ����ͼ��ͼ1��ʾ�� 3����ѹ����LC�����������

��ѹ����LC������Ҫ����4�����֣�ѹ��LC��·�� MC145152�����·�����ȴ�10-���²������Ƶ�ʷ�����·�� LM258��ɵĵ�ѹ�Ƚ�����·��

3.1ѹ��LC��·��VCO��

ѹ��LC��·(VCO)һ���ɷ���Ԫ����к͵�����ɡ����ڿɱ���ݶ����ܵĽ�����淴���ѹ�����Ӷ����٣��̴�������

��������

��

74 LS 164 3.9-3

068

2.5-2. P3-2 2.1-2. RET

3 �ķ�����

�� FIN FPGA

��

��

V-SVON-EN

MC145152

�ĸı䡣��Lһ��������Ƶ�ʵĵ��ڷ�Χ�ɶ����ܵ������仯��Χ�������費�ӵ�ѹU��ʱ�����������Ƶ��Ϊ����Ƶ�ʵĿɱ䷶Χ��4Y�����ݶ����ܵı��ݷ�Χ��AC����·���е���ΪC�������㹫ʽ4V��J��=1/2����C/C����Ҫ����15-35MHz�ı�Ƶ��ͼ��Lȡ 330nH������ݶ�������2-10V��������ΧӦΪ30~380pF��

�������������£�

����ͼ�ɵ���·�еĵ�Ч����Ϊ C=33.3+100��C

��CΪ���ݶ����ܵĽ���ݣ�

100+C

��f=15MHzʱ������=1/(2Ԫ/)�ɵ�

100C��10-)

1515000000 =1/(2#,/330��10-��(33.3 +

100+C

�ⷽ�̵�C,=375Pt��

��f=35MHzʱ������ͬ���ķ������C��=30pF��

��˱��������Ƶ��Ϊ15~35MHz�������ѹ�������ܵĽ���ݷ�ΧΪ30-375pF��

3.2������乤��ԭ��

����������ѡ��Ħ��������˾���������Ƶ�ʺϳ���ר��оƬMC145152�ο����������IJο�Ƶ������OSCin���پ����ڲ�R��Ƶ����Ƶ�����ź�J.����������Ϊ��Ƶ�ʡ���VCO�ļ��Ƶ�ʾ���������ˣ��پ���һ������������˫ģ��Ƶ�������� N=NP+A��Ƶ�����J��J.�͵��������뻧�������Ƶ��J�����бȽϣ������Ƶ�ʴ������ʱ���������ͻ����һ�����źŦ�R����V������źž���˥���˲�������ѹ�Ƚ���LM258�� LM258������һ����������ѹ��Ϊѹ��������Uc���Ӷ��ı� VCO�ڱ��ݶ����ܵĵ���ֵ������ı�VCO��Ƶ�ʣ�ֱ����������

MK FIN

DSCEN

RA 2-RA 0LD

��

ͼ1ϵͳ����ԭ����ͼ

ROUT

12.8N