基于VHDL设计的FPGA功能仿真结果与实际功能不一致问题研究

内容简介

数字执车与度用

数字执车与度用基于VHDL设计的FPGA功能仿真结果与实际功能不一致问题研究

金臻姜丽梅

(上海航天软件评测中心,上海201109)

应用研究

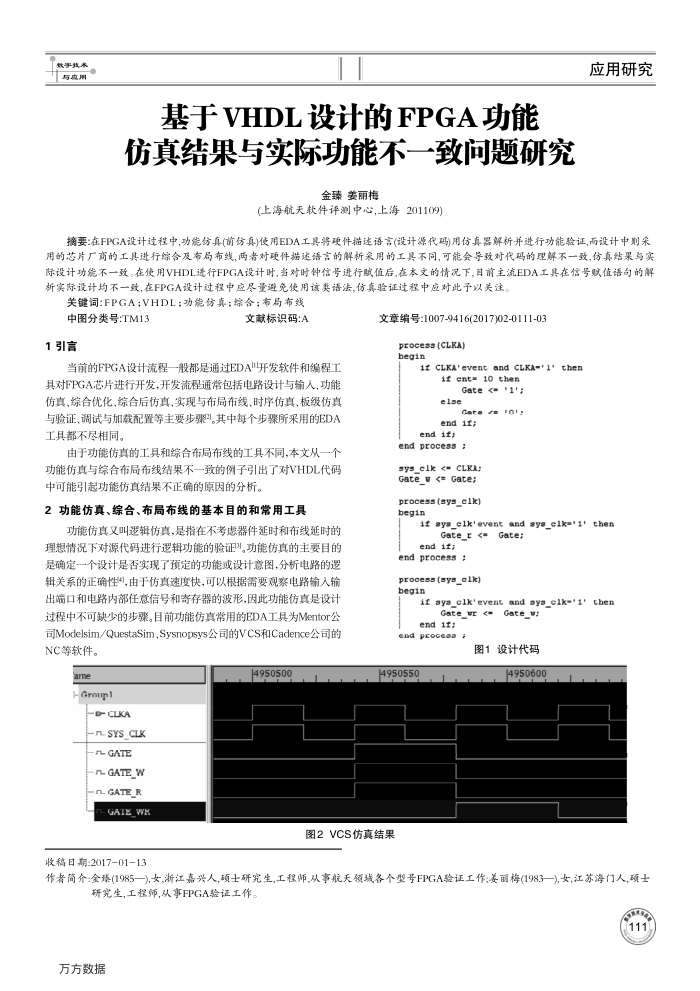

摘要:在FPGA设计过程中,功能仿真(前仿真)使用EDA工具将硬件描述语言(设计源代码)用仿真器解析并进行功能验证,而设计中荆采际设计功能不一致。在使用VHDL进行FPGA设计时,当对时钟信号进行赋值后,在本文的情况下,目前主流EDA工具在信号赋值语句的解新实际设计均不一致,在FPGA设计过程中应尽量避免使用该类语法,仿真验证过程中应对此予以关注。

关键词:FPGA;VHDL;功能仿真;综合;布局布线

中图分类号:TM13 1引言

文献标识码:A

当前的FPGA设计流程一般都是通过EDA"开发软件和编程工具对FPGA芯片进行开发,开发流程通常包括电路设计与输人,功能仿真、综合优化、综合后仿真、实现与布局布线、时序仿真、板级仿真与验证、调试与加载配置等主要步骤]。其中每个步骤所采用的EDA 工具都不尽相同。

由于功能仿真的工具和综合布局布线的工具不同,本文从一个功能仿真与综合布局布线结果不一致的例子引出了对VHDL代码中可能引起功能仿真结果不正确的原因的分析。

2功能仿真、综合、布局布线的基本目的和常用工具

功能仿真又叫逻辑仿真,是指在不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证。功能仿真的主要目的是确定一个设计是否实现了预定的功能或设计意图,分析电路的逻辑关系的正确性4),由于仿真速度快,可以根据需要观察电路输人输出端口和电路内部任意信号和寄存器的波形,因此功能仿真是设计过程中不可缺少的步骤。目前功能仿真常用的EDA工具为Mentor公司Modelsim/QuestaSim,Sysnopsys公司的VCS和Cadence公司的 NC等软件。

arne-Groupl

B- CLKA nSYS_CLK-GATE-几L GATE_W LGATE_R GATE_WK

收稿日期:2017-01-13

4950500

文章编号:1007-9416(2017)02-0111-03

prOCess (CLRA) begin

it CLKA'event and CLKA-'1' then

it ent= 10 then

Gate <= "1'; else

= 101

Gate end if;

end if, end process :

sys_elk <- CLKA; Gate_v <= Gate;

process (sys_elk) begin

it sys_elk'event and sys_elk='1' then

Gate_r < end if;

end process : process (sys_olk) begin

Gate;

if sys_clk'event and sys_clk-'i' then

Gate_wr <-

end if; end proceaa

Gate_u

图1设计代码

4950550

图2VCS仿真结果

14950600

作者简介:金臻(1985一),女,浙江嘉兴人,硕士研究生,工程师,从事航天领城各个型号FPGA验证工作;姜丽梅(1983一),女,江苏海门人,硕士

研究生,工程师,从事FPGA验证工作。

111

万方数据