您当前的位置:首页>论文资料>北斗基带芯片中的ARM控制单元设计

内容简介

数控技术

数控技术北斗基带芯片中的ARM控制单元设计

张泽军林平分

(北京工业大学嵌入式系统重点实验室北京100124)

数事教每皮人

摘要:北斗卫星导航接收机包含天线、RF模块、A/D和北斗卫星导航基带芯片等部分,而北母基等芯片由基带硬件处理单元、SoC控制逐辑单元和数据处理及PVT解算单元组成。本文对北半基带芯片中的SoC控制单元进行研究,设计中采用ARM7TDMI内核,模块化设计并集成,最终在FPGA原型平台上验证实现,为北十基带芯片的下一步开发做了充分准备以及保证了将来流片的成功率。

关键调:北丰卫星导航FPGA原型平台SoC

中图分类号:TN47 1、引言

文献标识码:A

文章编号:1007-9416(2012)03-0020-02

运行基带算法程序,将基带信号经过解调得到导航数据、PVT解

我国现在的卫星定位系统处于发展阶段,目前国内很多公司正在着力于北斗卫星导航芯片的研发,不久的将来我国会拥有自主知识产权的北斗卫星导航芯片。基于此现状,本文对北斗卫星导航芯片中的一部分单元进行研究与设计。

北斗卫星导航接收机包含天线、RF模块、A/D、北斗基带芯片等部分,而北斗基带芯片由基带硬件处理单元、SoC控制系统单元、数据处理及PVT解算单元组成。基带硬件处理单元包括捕获和跟踪两部分,捕获意味着找到一个确定的卫量信号(获取载波频率及扩频码相位信息);跟踪主要是发现导航数据相位的变化,这两部分般是由硬件实现。SoC控制系统单元负责控制基带芯片完成对卫星信号的捕获,后将捕获结果回送至跟踪模块实现实时跟踪,同时

+

clera

23ON t

MMU 主

RRN

主

西南面克更更面

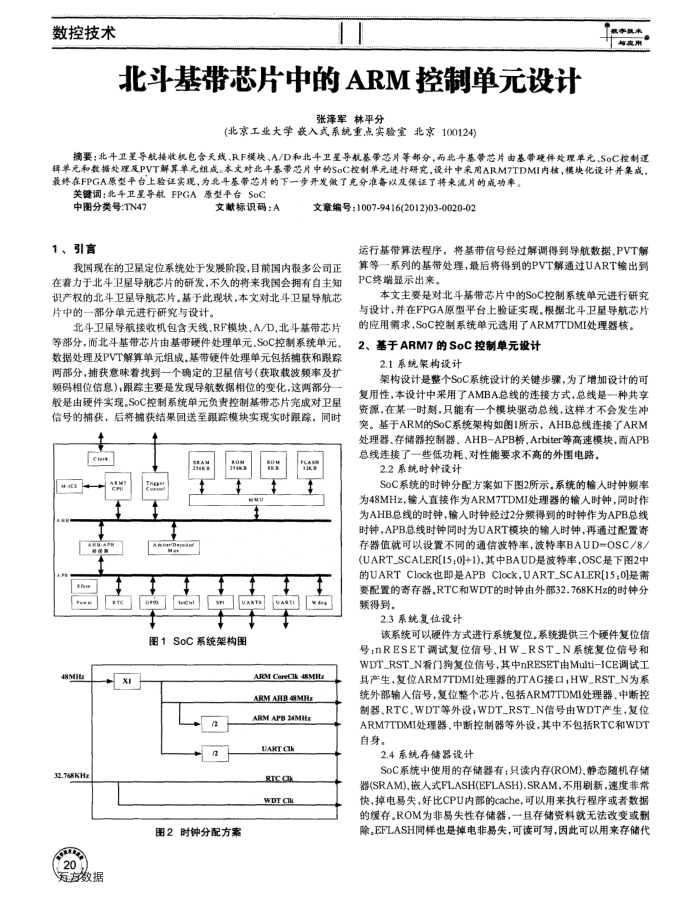

图1Soc系统架构图

48MHz 32.768KHz 20

有方数据

xI

图2时钟分配方案

ARM CoreCIk 48MHz ARMAHB48MHz ARM APB 24MHz

UARTCIK BIC.Ck WDTCak

算等一系列的基带处理,最后将得到的PVT解通过UART输出到 PC终端显示出来。

本文主要是对北斗基带芯片中的SoC控制系统单元进行研究与设计,并在FPGA原型平台上验证实现。根据北斗卫星导航芯片的应用需求,SoC控制系统单元选用了ARM7TDMI处理器核。 2、基于ARM7的SoC控制单元设计

2.1系统架构设计

架构设计是整个SoC系统设计的关键步骤,为了增加设计的可复用性,本设计中采用了AMBA总线的连接方式,总线是一种共享资源,在某一时刻,只能有一个模块驱动总线,这样才不会发生冲突。基于ARM的SoC系统架构如图1所示,AHB总线连接了ARM 处理器、存储器控制器、AHB-APB桥、Arbiter等高速模块,面APB 总线连接了一些低功耗、对性能要求不高的外围电路。

2.2系统时钟设计

SoC系统的时钟分配方案如下图2所示,系统的输入时钟频率为48MHz,输人直接作为ARM7TDMI处理器的输人时钟,同时作为AHB总线的时钟,输入时钟经过2分频得到的时钟作为APB总线时钟,APB总线时钟同时为UART模块的输入时钟,再通过配置寄存器值就可以设置不同的通信波特率,波特率BAUD=OSC/8/(UART_SCALER[15:0]+1),其中BAUD是波特率,OSC是下图2中的UART Clock也即是APB Clock,UART_SCALER[15:0]是需要配置的寄存器,RTC和WDT的时钟由外部32.768KHz的时钟分频得到。

2.3系统复位设计

该系统可以硬件方式进行系统复位。系统提供三个硬件复位信号:nRESET调试复位信号、HW_RST_N系统复位信号和 WDT_RST_N看门狗复位信号,其中nRESET由Multi-ICE调试工具产生,复位ARM7TDMI处理器的JTAG接口,HW_RST_N为系统外部输人信号,复位整个芯片,包括ARM7TDMI处理器、中断控制器.RTC.WDT等外设,WDT_RST_N信号由WDT产生,复位 ARM7TDMI处理器,中断控制器等外设,其中不包括RTC和WDT 自身。

2.4系统存储器设计

SoC系统中使用的存储器有:只读内存(ROM)、静态随机存储器(SRAM)、嵌人式FLASH(EFLASH).SRAM,不用刷新,速度非常快,掉电易失,好比CPU内部的cache,可以用来执行程序或者数据的缓存。ROM为非易失性存储器,一且存储资料就无法改变或删除。EFLASH同样也是掉电非易失,可读可写,因此可以用来存储代

上一章:PC机基于EPP接口的总线式硬件扩展

下一章:UWB室内定位技术研究