����ǰ��λ�ã���ҳ>��������>PC������EPP�ӿڵ�����ʽӲ����չ

PC������EPP�ӿڵ�����ʽӲ����չ

���ݼ��

��IT������

��IT������PC������EPP�ӿڵ�����ʽӲ����չ

��

������������ѧ��е����ѧԺ

��������

116023)

���ּ�����Ӧ��

ժҪ���������������Ῠ��չPC��ֱ��Ӳ�����۲ɹ����з��ɱ����ϸߣ�Ӳ�����ԺͿ��������з��ƣ�����������ʵ��Ӧ�ò������á�����EPP�ӿڵ��������ⲿӲ����չ����ʹ���ܵ�����ʵ����EPP���ߵ�8λ��ַ���������ߵ�ת�ӣ��Ӷ��ɷ�ʹ��չ�ٽӶ����Ӳ������ȶ������߲忨ʽ���ڲ�Ӳ����չ����ɱ����ͣ�Ӧ�ø������Ƽ���Ϊֱ�ӣ��������Ը��ӷ�ʹ���÷�����ʵ����֤���������ã�ֵ���ڸ���ͼ��Ӧ�ã�

�ؼ��ʣ�EPP

�ջ�

��ͼ����ţ�TP3

ֱ��Ӳ������

���߽ӿ����ױ�ʶ�룬A

1��

�ִ����������ٶȣ��洢�ݾ������������ȸ������Ѿ��õ��˼������ǿ��Ψ��ֱ��Ӳ����չ�����ı䲻��ĸ�����߲�������ǰ����PC����Ӧ��ϵͳ��ֱ�ӷü���Ƶ�Ӳ��������Ҫ��չ��ʽ����Ӧ����ܷ��㣬�����۲ɹ����з��ɱ����ϸߣ�Ӳ�����ú���������Ҳ�������ƣ����ڼ�ʵ��Ӧ�ò������ã�EPP�ǻ���PC��ԭ��ӡ���ӿڵ���ǿ���ж˿ڣ�����ͨ�������Ķ˿ڿ���ʵ��˫�����ݴ��䣬���ǽӿ���ʽ������߲�ͬ��һ�㲻��ֱ�����ã�Ҳ���ʺ϶�Ӳ������չ�����ʵ��Ӧ

nlow nWRITE

nIDalaStrobc nWAIT

DATA [7,0]

JIEPP-DB25

o o

o o

0

������(a)�������

Χ1

���±�ţ�1007-9416(2010)08-0041-02

�ò��ࡣ�������ʵ������γɱ��ⲿ�������ߣ�����չ���Ӹ���ʵ��Ӳ����Ӧ���豸ʵ��PC�����µ���Ӽ������ƽ�ʮ�ַ��㡣

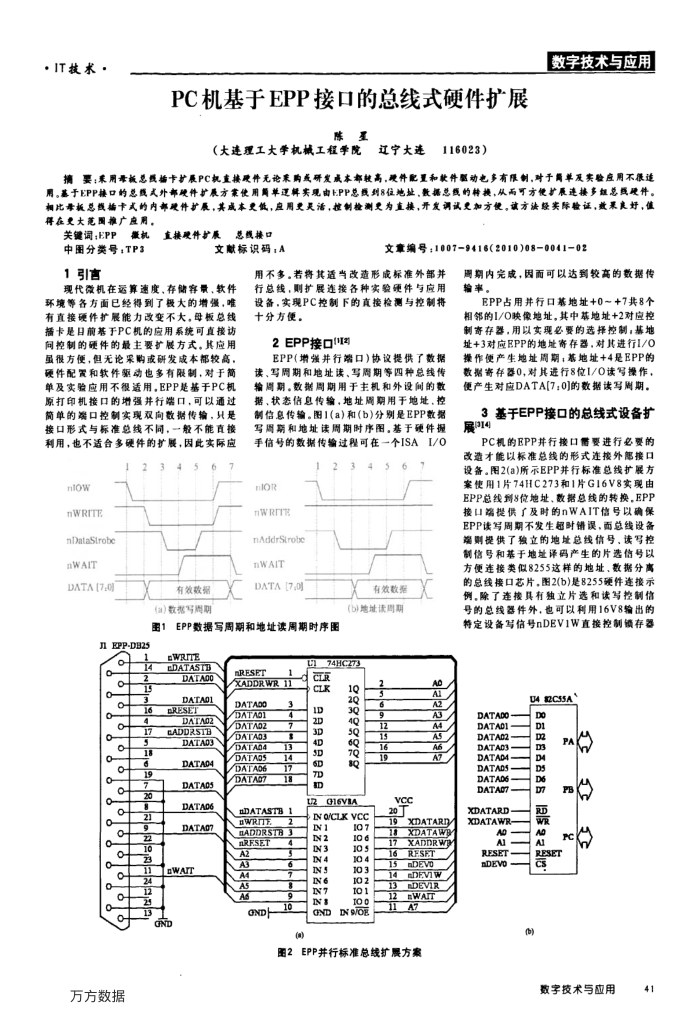

2EPP�ӿ�

EPP(��ǿ���ж˿ڣ�Э���ṩ�����ݶ���д���ں͵�ַ����д���ڵ��������ߴ������ڡ����������������������������ݡ�״̬��Ϣ���䣬��ַ�������ڵ�ַ��������Ϣ���䡣ͼ1(a)��(b)�ֱ���EPP����д���ں͵�ַ������ʱ��ͼ������Ӳ�������źŵ����ݴ�����̿���һ��ISAI/O

nIOR nWRR

nAddrS(robc WAIT

DATA[7,]

EPP����д���ں͵�ַ������ʱ��ͼ

nWRTE

EDATASTB DATAOO DATAO1

16

o Q o o 0 o 0

0

o 0

o

0 a 0 0 0 0 0

������

17 18 19 20

10 23 11 24 12 2 13

ERESEI

DATAG2 EADDRSTB

DATAD3 DATA04 DATA05 DATAD6 DATAO?

ewArT

D

BRESFT

XADDRWR1

DATAOO LOVLVG DATAOZ DATA03 DATA04

DATA05 DATADG DATAOT

14

S BWRTTF

BADDRSTB nRFSE

A A3 A4 A5 A

ONDH

10

p CLK

1D ̨ e

��Ч����(b)��ַ������

1Q 1 108 8Q

G16VBA 2

EN O/CLKVCC

N2 S N6

ND()

DNSVOE

vcc 20

0

AO A3 A

A7

XDATARI XDATAW9 XADDRW

RESET DEVO DEVIW BDEVIA EWATT A7

EPP���б�������չ����ͼ2

��������ɣ�������Դﵽ�ϸߵ����ݴ����ʡ�

EPPռ�ò��пڻ���ַ+0~+7��8�����ڵ�1/Oӳ���ַ�����л���ַ+2��Ӧ�����ʴ���������ʵ�ֱ�Ҫ��ѡ����ƣ�����ַ+3��ӦEPP�ĵ�ַ�Ĵ������������I/O �����������ַ���ڣ�����ַ+4��EPP�����ݼĴ���0������ѡ��8λ1/O��д�������������ӦDATA[7��0]�����ݶ�д�ڡ�

����EPP�ӿڵ�����ʽ�豸�� 3

չ314

PC����EPP���нӿ���Ҫ���б�Ҫ�ĸ�������Ա����ߵ���ʽ�����ⲿ�ӿ��豸��ͼ2(a)��ʾEPP���б�������չ����ʹ��1Ƭ74HC273��1ƬG16V8ʵ���� EPP���ߵ�8λ��ַ���������ߵ�ת����EPP �ӿڶ��ṩ�˼�ʱ��nWAIT�ź���ȷ�� EPP��д���ڲ�������ʱ�����������豸�����ṩ�˶����ĵ�ַ�����źš���д�����źźͻ��ڵ�ַ���������Ƭѡ�ź��Է�����������8255�����ĵ�ַ�����ݷ�������߽ӿ�оƬ��ͼ2(b)��8255Ӳ������ʾ�����������Ӿ��ж���Ƭѡ�Ͷ�д�����źŵ����������⣬Ҳ��������16V8������ض��豸д�ź�nDEV1Wֱ�ӿ��Ƽ�����

D482C55A Do

Tovia DATA02 DATAO3 DATAD4 DATADS-

DATA07 XDATAWR

A0 Al RESET nDEVO

m

PA 8

D7 wR A0 A1

()

PB PC

n n

���ּ�����Ӧ��

41

��һ�£�PTN���ϵĴ���

��һ�£���������оƬ�е�ARM���Ƶ�Ԫ���

�������

����RS485���ߵ�PC�뵥Ƭ�����ͨ��ϵͳ���

����PS��2�ӿڵ����и��������ϵͳ������չ���о�

����FPGA��CPCI���߽ӿ���Ʒ�����ѧϰ̽��

���� PC�����ڻ���⼼�����䱸FANUCϵͳ�����ػ����е�ʵ��

���� Linux�ĵ�����и��������ϵͳ��PC��-��Ƭ��������˫��ͨ��

����Linux�ĵ�����и��������ϵͳ��PC��-��Ƭ��������˫��ͨ��

����ISA���ߵĵ�����и�����ӿڵ�·����Ƽ��о�

����AT89S2051��Ƭ������ͨ�Žӿڵ�I�MO��չ�����о�