����Logistic����ģ�͵�Ӳ������оƬ�㷨������FPGAʵ��

���ݼ��

�㷨����

�㷨������������������

����Logistic����ģ�͵�Ӳ������оƬ�㷨����

��FPGAʵ��

�������

����ְҵ����ѧԺ������ͨ�Ź���ѧԺ�㶫�518055)

ȷҪ�������Ϣ��ȫ��ǵ�Ӧ�ã�ͨ����Logistic��ϴģ�͵ķ��������������һ����Ӳ��ʵ�ֵĸ���Logistic������㷨�������ٶȿ�ɱ��ͣ���ȫ�Ըߡ������Ժõ��ŵ㡣����������������Logistic���������㷨�������һ�����FPGA�����ݼ���оƬ��ƣ����Ը�оƬ�������ٶȺ�Ч���ķ�����֤���˸�оƬ��ʵ���ԡ�

�ؼ��ʣ�Logistic�������оƬFPGA

��ͼ����ţ�TN918

���ױ�ʶ�룺A

���±�ţ�1007-9416(2011)11-0126-03

������Ϣ������ͻ���ͽ�����Ϣ��ȫ����Ҳ����ͻ����Ϊ��ʹ��Ϣ�ڴ��ݹ����в�����ȡ��ͨ����Ҫ���ü��ܼ��������ڼ��ܼ����У�������֮ǰ�����ݱ���Ϊ"���ġ�������֮������ݱ����������ġ��������ڼ��ܼ���ͽ��ܼ���������֮Ϊ����Կ�������������Ƿ����Զ���ѧϵͳ���е�һ���˶���ʽ�����в�ȷ���ԣ���ֵ�����Ժͳ��ڲ���Ԥ���ԵȰ�ȫ������ʹ��������ѧ֮��������Ȼ����ϵ�У��ڼ��ܼ������������о���ʮ������������ѧ���ԣ���������ѧ�ѳ�Ϊ�ִ�����ѧ����Ҫ�о�����"������ӳ�������Dz���α��������к���Ҫ���ܵĶ������һ���ض������õ������ݣ���ʵ���Ͽ�������ӳ��õ�������������������У�����кܺõ�����������ԣ���˿�����������α����źŻ�α����롣Logis-tic��ӳ��ģ����һ�ַdz���ȴ���㷺Ӧ�õľ������ӳ��ģ��)

Ӳ�����ܼ�����һ��ʮ����Ч�ļ��ܼ�������ͳ�ļ��ܹ�����ͨ�������������м�������ʵ�ֵģ����ַ�������ռ��������Դ�⣬�������ٶȽ�������ȫ��Ҳ�ϲ����������Logistic����ģ�ͣ���Ƴ���һ������Ӳ��ʵ�ֵļ����㷨����ͨ��FPGA��֤�˸��㷨�ļ���Ч���������е�Ӳ��������ȴ�ͳ���������ܾ��м����ٶȿ죬��ȫ�Ըߣ��Լ۱ȸߵ��ŵ㣬���Ҿ��зdz��õ�Ӧ��ǰ����

1������оƬ�㷨���

1.1Logistic����ԭ������ģ��

Logistic�ǻ���ģ���бȽϾ����һ�֣�����Դ�ڳ��ģ��

(wormnumbermodel)

X++ =uX,

(1)

(1)ʽ��Xk+1Ϊ��һ�����ӵ���������XkΪ��һ�����ӵ����������Ǹ�������������������ʵ���г��ӵ�ʳ����⣬����ռ����⣬��������ȵȣ���ʵ����������֮���������ϵ���Ա�ʾΪ

(2)ʽ:

X,- =uX, (1Xx)

(2

(2)ʽ������ν��Logisticģ�ͣ��о������ʾ����(2)ʽ�е�u ��Xk�����ϵ��3.5699u4,0

����Logistic����ģ������Ӧ����ѧģ�͵Ķ����Ϊȫ��ʵ������������Ӳ��������Ҫʹ����ɢ�����ݣ�������Ҫ��Logistic����ģ����ӳ���ϵ�Ķ���Ǵ�ʵ����ӳ�䵽�����ǡ�

�������ἰ��Ӳ������װ�ò���ʽ(2)��Ϊ����ܵĺ���ԭ������uΪ���룬��XkΪ��������������С�Ϊ����Ӧ�����㷨�Ĺ㷺Ӧ�ã���Ҫ��u��Xk������һ��ӳ����Logistic�����������ǵĶ�����С�

1126 ������

���⣬���ڼ����ϵͳ�������ɢ�ͣ���Ҫ��Logistic������������ɢ�����ڱ�����������������8λ�Ķ����������У���ΪM��������16λ�Ķ�����������ΪK����

ME[0,255].KE[0,65535]

�����ԭʼ��ʽ(2)���������������ϵ�ӳ���ϵ��

k=0.4301K/65535+3.5699,k [3.5699,4] m=M/256,m E (0,1)

(3)(4)

������������ȡֵ��ϵ�������k��m������ΪLogistic�����㷨ӳ���ϵ���Ա������ˣ�

X++ =uXx (1 Xx) = km(1 m)

(5

��N��Mһ������һ��8λ���������ݣ���n=N/256;nE��0��1)������(5)���Եõ������㷨�����㹫ʽ��

N=234(440+K+239571933)(255M)+M

(6)

����(6)ʽ��Ϊ���������õ��㷨���������ݡ����ó�ʼ��M�����Եõ���һ��N���ٰ�N��ΪM����(6)�����Եõ��ڶ���N���������ƣ����Եõ�һ����������С����ڱ������Dz�����ˮ��(Pipeline)���㣬��˽����ʹ���ˮ��(IterationPipeline������������ѡ����ˮ�ߵļ��㣬���Եõ������õ�������������ʵ�ּ��ܡ� 2������оƬ��FPGAʵ��

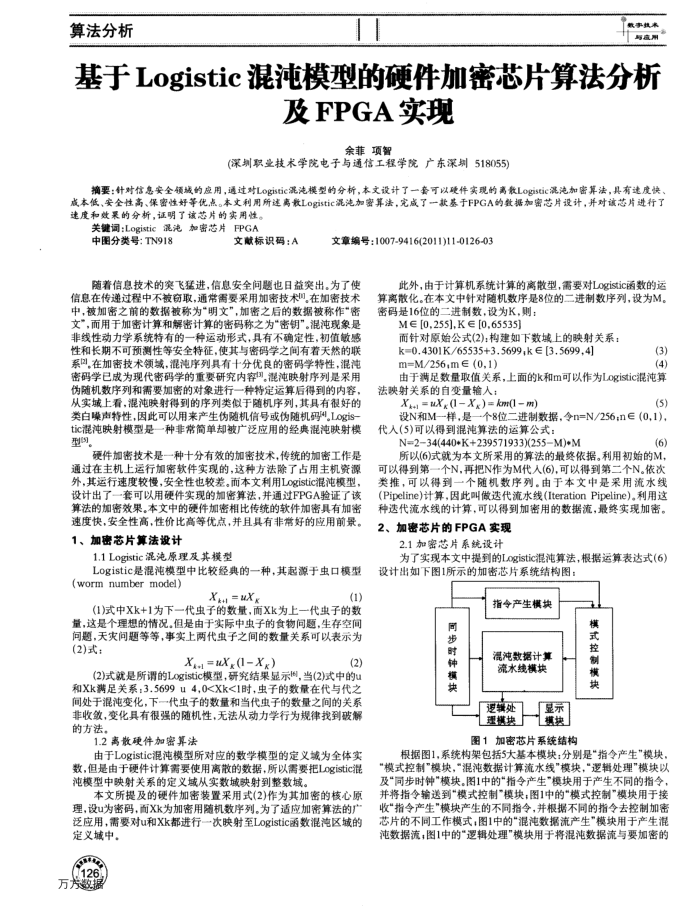

2.1����оƬϵͳ���

Ϊ��ʵ�ֱ������ᵽ��Logistic�����㷨�������������ʽ��6����Ƴ�����ͼ1��ʾ�ļ���оƬϵͳ�ṹͼ

ָ��������

�䲽ʱ�Ӻ��

�������ݼ�����ˮ��ģ��

�渨����ʾ��ģ�����

ͼ1����оƬϵͳ�ṹ

��ʽ���ƺ��

����ͼ1��ϵͳ���ܰ���5�����ģ�飺�ֱ���"ָ�����"ģ�飬"ģʽ����"ģ�飬�������ݼ�����ˮ��"ģ�飬��������"ģ���Լ���ͬ��ʱ�ӡ�ģ�顣ͼ1�еġ�ָ�����"ģ�����ڲ�����ͬ��ָ�����ָ�����͵���ģʽ����"ģ�飺ͼ1�еġ�ģʽ����"ģ�����ڽ���"ָ�����"ģ������IJ�ָͬ������ݲ�ͬ��ָ��ȥ���Ƽ���оƬ�IJ�ͬ����ģʽ��ͼ1�еġ���������������"ģ�����ڲ���������������ͼ1�еġ���������ģ�����ڽ�������������Ҫ���ܵ�