您当前的位置:首页>论文资料>基于FPGA技术的FIR数字滤波器的设计

基于FPGA技术的FIR数字滤波器的设计

内容简介

应用研究

应用研究基于FPGA技术的FIR数字滤波器的设计

李俊,刘准霞1朱丹1贺曼2

(1.安徽理工大学电气与信息工程学院安徽淮南232001;2.西安交通大学电气工程学院陕西西安710049)

摘要:在数字化技术在各个领成得到广泛运用的今天,数字滤波器是数字系统中信号处理关键的一环。数字滤波器和模拟滤波器相比具有更高的精度、信噪比,以及不可比拟的可鑫性。由于在性能、成本、灵活性和功耗等方面的优势,基于FPGA的信号处理器已广泛应用于各种信号处理领域。本文主要介缩了基于现场可编程门阵列(FPGA股术FIR数宇滤流器的设计,该方法通过DSPBuilder和MATLAB等款件进行开发、仿具和验证,使之使于在FPGA中实观。

关键调:数宇滤波器现场可编程门阵列FIRDSPBuilderMATLAB:

中图分类号:TN820

文献标识码:A

文编号:1007-9416(2012)02-0104-03

通常在信号产生、采集、传输过程中产生杂波和噪声,通常需要加人滤波器将干扰无用的噪声或者不需要额段的信号滤除。数字滤波器和模拟滤波器相比具有更高的精度、信噪比,以及不可比拟的可靠性只要适当改变数字滤波程序有关参数,就能方便的改变滤波特性,因此数字滤波使用时方便灵活,

由于在性能、成本,灵活性和功耗等方面的优势,基于FPGA的信号处理器已广泛应用于各种信号处理领域。本文正是在此背景下研究基于FPGA技术,运用DSPBuilder和MATLAB等软件工具设

计工程中实用的FIR数字滤波器。 1、FIR数宇滤波器设计原理

有限长脉冲响应(FIR)滤波器的系统函数只有零点,除原点外,没有极点,因而FIR滤波器总是稳定的(2)

长度为M的因果有限冲激响应滤波器由传输函数H(z)描述:

维

h(k)z"*

H(z)s

它是次数为M-1的z-1的一个多项式。在时域中,上述有限冲

激响应滤波器的输人输出关系为: m)-h(k) (a-x)

其中x(n)是输人采样序列,h(i)是滤波器系数,y(n)表示滤波器的输出序列。

也可以用卷积来表示输出序列y(n)与x(n)、h(n)的关系。 y(n) =x(n)*h(n)

通常一个长度为M的有限冲激响应滤波器由M个系数描述,并

目需要M个要法器和(M-1)个双验人加法器来实现,

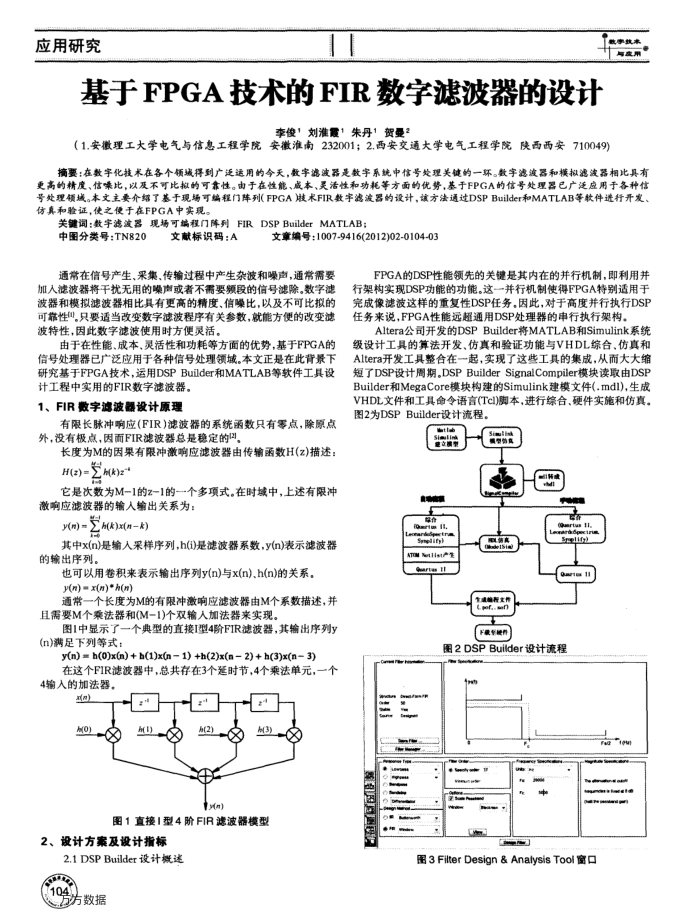

图1中显示了一个典型的直接I型4阶FIR滤波器,其输出序列y(n)满足下列等式:

y(n) = h(0)x(n) + b(1)x(n 1) +h(2)x(n 2) + h(3)x(n ~ 3)

在这个FIR滤波器中,总共存在3个延时节,4个乘法单元,一个 4输入的加法器。

(a)r(0)

n

图1直接I型4阶FIR滤波器模型

2、设计方案及设计指标

2.1DSPBuilder设计概述方数据

FPGA的DSP性能领先的关键是其内在的并行机制,即利用并行架构实现DSP功能的功能。这一并行机制使得FPGA特别适用于完成像滤波这样的重复性DSP任务,因此,对于高度并行执行DSP 任务来说,FPGA性能远超通用DSP处理器的审行执行架构。

Altera公司开发的DSPBuilder将MATLAB和Simulink系统级设计工具的算法开发、仿真和验证功能与VHDL综合、仿真和 Atera开发工具整合在-起,实现了这些工具的集成,从而大大维短了DSP设计周期。DSPBuilderSignalCompiler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成 VHDL文件和工具命令语言(Tcl)脚本,进行综合、硬件实施和仿真。图2为DSPBuilder设计流程。

CGuertus11

ATON NetHst产

F最Yen

图2DSPBuilder设计流程

图3FilterDesign&AnalysisTool窗口

上一章:基于FPGA的远程控制设计系统

下一章:基于FPGA的电压控制LC振荡器的设计研究