����ǰ��λ�ã���ҳ>��������>���� FPGA �� VGA ��Ϸ���

���� FPGA �� VGA ��Ϸ���

���ݼ��

�������������

�����������������FPGA��VGA��Ϸ���

���

(����ʦ����ѧ�����������ϢѧԺ�Ĵ��ϳ�637002)

��ƿ���

ժҪ�����ר����Ƶ����оƬʵ��VGAͼ���źŷ�����������Ƽ����Ѷȴ����ɱ��ߣ�����ƻ���FPGA����ʵ��VGAͼ���źŷ�������������VGA����ģ����ڲ��ṹ��ʵ����ˮƽʱ���ź���ơ���ֱʱ���ź���ơ�������ʾ����ƣ������Ծ��ɹ��ܿ��ƺ���ʾ������������ȷ��

�ؼ�����VGAFPGAͼ���źŷ�����

��ͼ����ţ�TP391.41 1��ǰ��

���ױ�ʶ�룺A

���±�ţ�1007-9416(2012)04-0171-02

ϵͳ������Ҫ�IJ�����VGAʱ��IJ�����VGAʱ����������

FPGA�������ɣ����ٶȡ����ġ����С���зḻ�IJ��ұ�(LUT)��Դ�������ֵ�·������еõ��㷺��Ӧ�á�����FPGA�ĵ�·������㣬�Լ۱ȸߣ����Կ˷�ģ�������������Բ��ȱ�㣬 VGA�ӿ�������ʾ������ͨ�ŵ�Ψһ�ӿڣ�ͨ��FPGA�������� RGB�źš���ͬ���źš���ͬ���źŵ��źţ��������йر���������ʵ�ֶ�VGA��ʾ���Ŀ��ơ�����EDA������Ʒ��������Ը����û�����Ҫ����Ƴ������ǿ��VGA��ʾ�����������Ҳ���Ҫ��������������ܹ���ͳɱ����ֿ�����������ʵ���в��ϱ仯��

��Ҫ��ͬʱ��Ʒ����������Ҳ����Ѹ�١� 2��ϵͳ����ԭ������ͼ

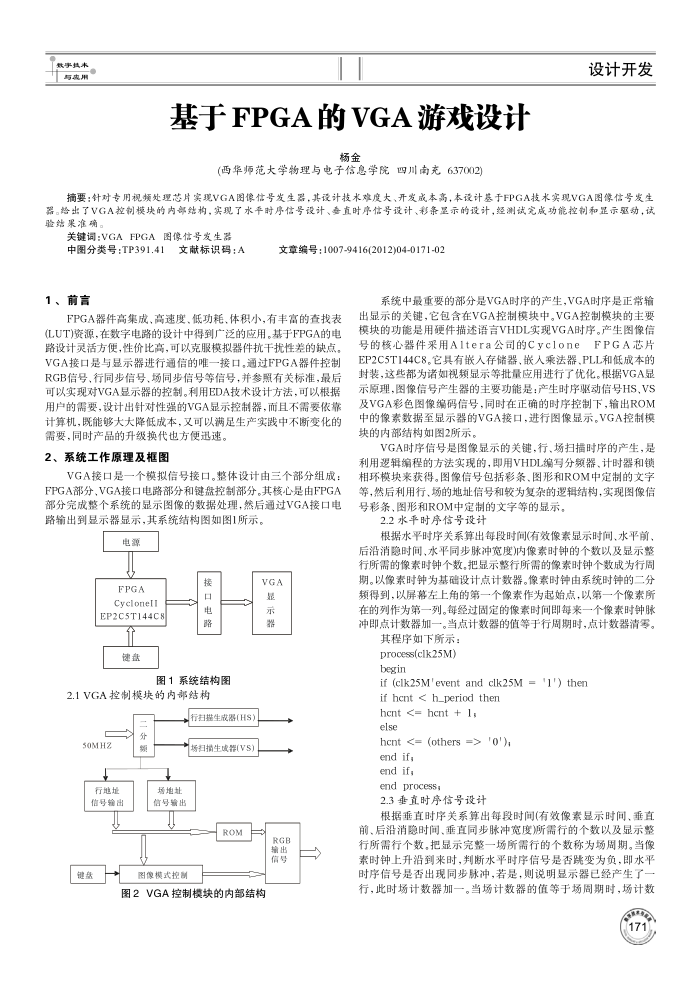

VGA�ӿ���һ��ģ���źŽӿڡ��������������������ɣ� FPGA���֣�VGA�ӿڵ�·���ֺͼ��̿��Ʋ��֡����������FPGA �����������ϵͳ����ʾͼ������ݴ�����Ȼ��ͨ��VGA�ӿڵ�·�������ʾ����ʾ����ϵͳ�ṹͼ��ͼ1��ʾ��

��Դ

FPGA Cyclonell

EP2C5T144C 8

����

�ӵ�·

ͼ1ϵͳ�ṹͼ

2.1VGA����ģ����ڲ��ṹ

��ɨ����������HS)

50MH2 �е�ַ�ź����

����

����ַ�ź����

������������(VS)

ROM

ͼ��ģʽ����

VGA ��ʾ��

RGB ����ź�

ͼ2VGA����ģ����ڲ��ṹ

����ʾ�Ĺؼ�����������VGA����ģ���С�VGA����ģ�����Ҫģ��Ĺ�������Ӳ����������VHDLʵ��VGAʱ����ͼ���źŵĺ�����������Altera��˾��cvclone

FPGAоƬ

EP2C5T144C8��������Ƕ��洢����Ƕ�˳˷�����PLL�͵ͳɱ��ķ�װ����Щ��Ϊ������Ƶ��ʾ������Ӧ�ý������Ż�������VGA��ʾԭ����ͼ���źŲ���������Ҫ�����ǣ�����ʱ�������ź�HS��VS ��VGA��ɫͼ������źţ�ͬʱ����ȷ��ʱ������£����ROM �е�������������ʾ����VGA�ӿڣ�����ͼ����ʾ��VGA����ģ����ڲ��ṹ��ͼ2��ʾ��

VGAʱ���ź���ͼ����ʾ�Ĺؼ����С���ɨ��ʱ��IJ���������������̵ķ���ʵ�ֵģ�����VHDL��д����������ʱ�������ģ������á�ͼ���źŰ���������ͼ�κ�ROM�ж��Ƶ����ֵȣ�Ȼ�������С����ĵ�ַ�źźͽ�Ϊ���ӵ����ṹ��ʵ��ͼ���źŲ�����ͼ�κ�ROM�ж��Ƶ����ֵȵ���ʾ��

2.2ˮƽʱ���ź����

����ˮƽʱ���ϵ���ÿ��ʱ��(��Ч������ʾʱ�䡢ˮƽǰ����������ʱ�䡢ˮƽͬ���������)������ʱ�ӵĸ����Լ���ʾ�������������ʱ�Ӹ���������ʾ�������������ʱ�Ӹ�����Ϊ�����ڡ�������ʱ��Ϊ������Ƶ������������ʱ����ϵͳʱ�ӵĶ���Ƶ�õ�������Ļ���Ͻǵĵ�һ��������Ϊ��ʼ�㣬�Ե�һ���������ڵ�����Ϊ��һ�С�ÿ�����̶�������ʱ�伴ÿ��һ������ʱ�����弴���������һ�������������ֵ����������ʱ������������㡣

�����������ʾ�� process(clk25M) begin

if (clk25M'event and clk25M = '1') then if hcnt < h_period then

hcnt <= hcnt + 1, else

hcnt <= (others => 'o'),

end if end if;

end process;

2.3��ֱʱ���ź����

���ݴ�ֱʱ���ϵ���ÿ��ʱ��(��Ч������ʾʱ�䡢��ֱǰ����������ʱ�䡢��ֱͬ���������)�����еĸ����Լ���ʾ���������и���������ʾ����һ�������еĸ�����Ϊ�����ڡ�������ʱ�������ص���ʱ���ж�ˮƽʱ���ź��Ƿ�����Ϊ������ˮƽʱ���ź��Ƿ����ͬ�����壬���ǣ���˵����ʾ���Ѿ��������У���ʱ����������һ��������������ֵ���ڳ�����ʱ��������

171

��һ�£�����FPGA�IJ���ƥ���㷨�Ľ��о�

��һ�£�����FPGA��Matlab��IP����Ʒ���