基于FPGA和Matlab的IP核设计方法

内容简介

设计开发

设计开发基于FPGA和Matlab的IP核设计方法

葛茂林

(北京工业大学软件学院北京100124)

与皮

摘要:为了简化IP核的设计过程,本文介绍了一种基于FPGA的中值滤波算法的IP核实现方法。针对FPGA的特点对实现方法进行了研究,从而简化了复杂算法的IP核设计问题。实验结累表明,该IP核设计方法具有设计周期,可靠性高等特点。

关键调:FPGAMatlabIP核

中图分类号TP2

文献标识码:A

文章编号:1007-9416(2013)03-0192-02

IP核即知识产权核,本质上是用于设计ASIC或者可程序设计器件的逻辑块。将一些数字电路中比较复杂的模块设计成可以修改参数的模块,提供给设计者或用户直接调用,这样能大大减轻设计的负担并且能够避免重复的劳动,缩短开发周期。IP核分为软核、固核以及硬核。软核只完成RTL级的行为设计,具有很大的灵活性,不受很多现实条件的制约,它以某种HDL源文件形式交给用户,它经过了行为级的优化和验证,不含有任何具体的物理信息。本文介

绍的就是软核的新的设计方法。 1传统的软IP核的设计方法

传统的IP核设计都是设计者通过直接编写硬件语言(VHDL)来实现的,对于一个复杂的系统(包含很多模块),纯释用硬件语言来描述需要很大的工作量。每个模块内部的设计,模块之间的设计以及时序,接口、电路的速度和面积等实际间题对设计者提出了很高的要求。总而言之,单纯用硬件语言去编写和实现复杂的IP核是相当困难的。

2一种高效的基于FPGA的IP核的实现

本文通过实现一个相对复杂的算法(中值滤波算法)IP核来介绍这种高效的方法。

2.1中值滤波原理

中值滤波法是一种典型的非线性平滑方法,使用该方法的目的是保护图像边缘的同时消去噪声的影响国。中值滤波的原理是把数字图像或数字序列中一点(x,Y的值用该点的一个邻域中各点值的中值代替,让周围的像素值接近真实的数值,从而能有效的消除脉冲噪声、概盐噪声等的影响,但同时文能保留图像的边缘信息,这是因为它不依赖于领域内那些与典型值差别很大的值4。

2.2图像处理基本平台的搭建【5]

本文中使用的是Xilinx的SP601系列FPGA,开发环境是Xilinx ISE13.1开发套件以及Matlab2010a。用FPGA来实现挑选9个像素值的中间值这个排序过程相当复杂,这里将使用一种近似的方法。首先将Matlab与Xilinx的开发工具包进行关联,Matlab的版本必须和SystemGenerator所支持的版本相同,否则无法关联。关联成功之后即可构建系统模型,进行直观的系统调试。在Simulink中可以使用基于图像的处理方式和基于数据流的处理方式,但是作为硬件设计,SystemGenerator只允许基于数据流的设计方式。

在System Generator下搭建的图像处理平台lnlSystem Gen erator模块是必不可少的,它负责整个系统的时钟HDL代码以及网表的生成。同时也可以通过修改它的设置来配置开发板的型号和存储路径等。对输人模块进行参数修改,图像在模块间是以一维数组形式传递的,采样时间为连续采样,间隔时间设置为0;不需要中断检测,使用过零检测。对输出模块进行参数修改,都在采用默认设置即可。接下来对需要缩写程序使得图像能够在输人输出模块中传递。在空白处单击鼠标右键选择ModelProperties选项,对 PreLoadFcn和StopFcn两个回调函数进行编写,它们的用途分别是读取图像数据和显示图像17]

PreLoadFcn部分函数编写如下: 192

In2D=imread("图片路径名称.png"),%读取图像数据

ImageWidth=size(In2D,2),ImageHeight=size(In2D, 1);%读取图像长宽

In1D=reshape(In2D, 1,ImageWidth+ImageHeight),%形成要求的数据格式

InID-[double(o: ImageWidth+ ImageHeight1') double(InID)";

StopFcn部分函数编写如下:

Out2D=reshape(OutlD(Latency Latency+ImageWidth+ImageHeight1),ImageHeight, ImageWidth),%将一维数组转成二维数组

h=figue,clf,Set(h,'name','result");

都设置完之后运行模拟,从结果中可以看出输出的图像和输人的图像是完全一样的,说明二维图像以一维数组的形式在系统中传输,也证明了系统平台的正确性。

2.3中值滤液模型平台的搭建

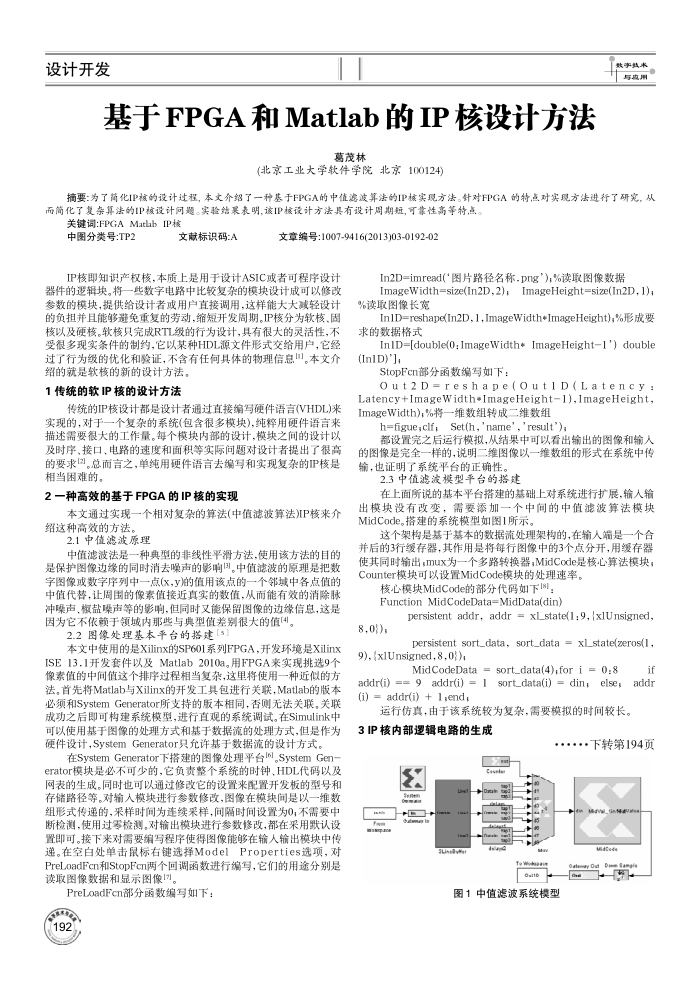

在上面所说的基本平台措建的基础上对系统进行扩展,输人输出模块没有改变,需要添加一个中间的中值滤波算法模块 MidCode。搭建的系统模型如图1所示。

这个架构是基于基本的数据流处理架构的,在输人端是一个合并后的3行缓存器,其作用是将每行图像中的3个点分开,用缓存器使其同时输出;mux为一个多路转换器;MidCode是核心算法模块; Counter模块可以设置MidCode模块的处理速率。

核-心模块MidCode的部分代码如下181: Function MidCodeData=MidData(din)

8.0)

persistent addr, addr = xl_state(1: 9, (xlUnsigned, persistent sort_data, sort_data = xl_state(zeros(1,

9), (xlUnsigned,8,0),

MidCodeData

addr(i) == 9 addr(i) = 1(i) = addr(i) + 1send,;

sort_data(4),for i = 0:8

if

sort_data(i) = din,

else,addr

运行仿真,由于该系统较为复杂,需要模拟的时间较长。 3IP核内部逻辑电路的生成

.・.下转第194页

网

Cenle

Sa

n i

s

Lse

woha

图1中值滤波系统模型