您当前的位置:首页>论文资料>基于CPLD∕FPGA的CPU设计

内容简介

设计开发

设计开发基于CPLD/FPGA的 CPU设计

刘景文

(天津滨海职业学院天津300451)

数事费。与度用

摘要:在分析CPU选型基础上,确定设计基于CPLD/FPGA的8住字长、RISC、多周期、哈佛架构CPU。通过CPU体系结构设计、CPU指令系统的设计,描述了CPU设计相关同题。

关键调:CPLD/FPGASOC指令系统体系结构

中图分类号TN702 1引言

文献标识码:A

文章编号:1007-9416(2014)02-0162-02

3CPU体系结构设计

随着EDA技术的发展,用硬件描述语言设计以PLD/FPGA为载体进行各种数字电路设计成为一种不可阻挡的趋势,用硬件描述语言设计CPU也成为可能伴随作为载体的PLD/FPGA技术飞速发展,PLD/FPGA器件内集成成千上万个门,在CPLD/FPGA上不仅可以容纳CPU,还可以CPU工作所需要的外图电路,发展成为 SOC技术,设计实现CPU是这项技术的核心。

SOC技术有多种现成产品,CPLD/FPGA生产厂家多提供SOC 解决方案。如Atera为业界提供多种软核处理器,从软核处理器 Nios到ARM和Freescale流行的体系结构,另一CPLD/FPGA 生产厂家Xilinx也提供了类似产品。这些SOC最大特点是,它们仅针对各自厂家自已的FPGA产品,没有通用性。面设计可在不同厂家CPLD或FPGA上运行、通用SOC具有现实意义,这就是设计基于 CPLD/FPGA的CPU,

CPU设计涉及:CPU类型的选取,CPU体系结构设计,CPU指令系统的设计、CPU设计、CPU检验和CPU应用五个方面内容。 2CPU设计选型

CPU类型选取涉及四个方面:选择CPU的字长,CPU的指令类型、CPU指令执行的周期类型,CPU架构。

CPU类型按字长分为8、16.32.64位等类型。CPU字长越长,处理数据的能力越强,但所需要的资源越多

CPU类型按的指令集类型可分为CISC和RISC两类。在进行 CPU设计时,CISC和RISC两者的主要区别为指令的长度和指令的多少。相对而言RISC类型CPU指令较少,每条指令的长度相同。选择不同指令类型,会直接影响CPU指令译码部分的设计难度,选择 RISC类型CPU时,可以降低指令译码部分的设计难度。

CPU类型按指令执行的时间周期类型可分为单周期和多周期两类。要进行指令执行单周期CPU设计,涉及流水线、缓存等现代计算机设计相关概念,选择多周期CPU则相对简单。

CPU类型按CPU架构分为哈佛架构和普林斯顿架构两类,善林斯额架构CPU将指令和数据放在同一存储器内,哈佛架构CPU 的存储器分为指令存储器和数据存储器两部分。选择哈佛架构可以相对减少指令的条数

在进行CPU类型的选取时.除考虑涉及四个方面外,CPU的用途也是一个重要的考虑因素,综合考虑,选择设计8位字长,RISC,多周期、哈佛架构CPU。

在确定设计8位字长,RISC、多周期、哈佛架构CPU后,首先要进行CPU体系结构的规划设计。概念上,传统计算机由控制器,运算器、存储器、输人设备、输出设备五部分组成,控制器和运算器被制作在一起,称为CPU,CPU体系结构设计主要是运算器部分的规划,CPU设计主要是控制器设计运算器中ALU部分设计、运算器数据通道的设计

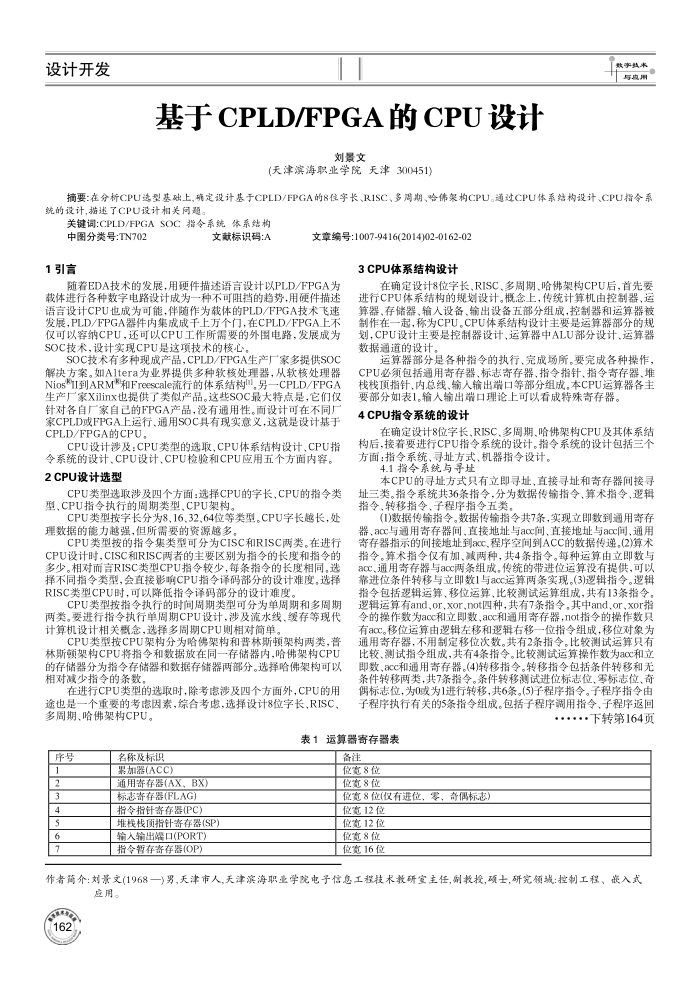

运算器部分是各种指令的执行、完成场所。要完成各种操作, CPU必须包括通用寄存器、标志寄存器、指令指针、指令寄存器、堆栈栈顶指针、内总线,输人输出端口等部分组成。本CPU运算器各主

要部分如表1。输人输出端口理论上可以看成特殊奇寄存器。 4CPU指令系统的设计

在确定设计8位字长,RISC、多周期、哈佛架构CPU及其体系结构后,接着要进行CPU指令系统的设计。指令系统的设计包括三个方面:指令系统、寻址方式、机器指令设计。

4.1指合系统与导址

本CPU的寻址方式只有立即寻址,直接寻址和寄存器间接寻址三类。指令系统共36条指令,分为数据传输指令、算术指令、逻辑指令、转移指令、子程序指令五类

(1)数据传输指令。数据传输指令共7条,实现立即数到通用寄存器、acc与通用奇存器间,直接地址与acc间、直接地址与acc间、通用寄存器指示的间接地址到acc.程序空间到ACC的数据传递,(2)算术指令。算术指令仅有加、减两种,共4条指令。每种运算由立即数与 acc、通用寄存器与acc两条组成。传统的带进位运算没有提供,可以靠进位条件转移与立即数1与acc运算两条实现。(3)逻辑指令。逻辑指令包括逻辑运算、移位运算、比较测试运算组成,共有13条指令,逻辑运算有and.or、xor.not四种,共有7条指令。其中and.or,xor指令的操作数为acc和立即数,acc和通用寄存器,not指令的操作数只有acc。移位运算由逻辑左移和逻辑右移一位指令组成,移位对象为通用寄存器,不用制定移位次数。共有2条指令。比较测试运算只有比较、测试指令组成,共有4条指令。比较测试运算操作数为ac和立即数,acc和通用寄存器。(4)转移指令。转移指令包括条件转移和无条件转移两类,共7条指令。条件转移测试进位标志位、零标志位、奇偶标志位,为0或为1进行转移,共6条。(5)子程序指令。子程序指令由子程序执行有关的5条指令组成。包括子程序调用指令、子程序返回

·.下转第164页

表1运算器寄存器表

库号 2 3 4 5 6 7

名称及标识累加器(ACC)

通用寄存器(AX,BX) 标志寄存器(FLAG) 指令指针寄存器(PC)

堆栈栈顶指针客存器(SP) 输人输出螺口(PORT) 指令暂存寄存器(OP

备注宽8位位宽8位

位宽8位(仅有进位,零,奇偶标志)

位宽12位位宽12位位宽8位位宽16位

作者简介:刘景文(1968一)男,天津市人,天津滨海职业学院电子信息工程技术教研宝主任,制教投,颈士,研究领城:控制工程、嵌入式

应用。

162