基于MCU﹢FPGA架构的红外与电视共享显存OSD系统设计

内容简介

设计开发

设计开发基于MCU+FPGA架构的

红外与电视共享显存OSD系统设计

齐蛮洲

(湖北久之洋红外系统股份有限公司湖北武汉430223)

数事共与庆用

摘要:介绍一种基于MCU+FPGA案构的OSD系统的硬件设计与软件实境该方案使用FPGA内部两个效口RAM构建显存模块,被叠加的数据信息势存在该是存中,通过MCU刷新数据信息以更受新字符内容并改变其位置。在红外视频与电视视频之间切换时,FPGA内部逻辑控制电路部寻址该双口 RAM以完成字符叠加,从而实OSD功能。这种设计技巧的优点在于节省了宝资的FPGA片上存储资源,有利于扩展到多通道视频OSD应用中。本方案具有架构扩展性好、源代码组缺简单,宇符内容及量示位置修灵活的优点川。

关键词:FPGAOSD字并叠加红外视频电视中图分类号:TN919.8

文献标识码:A

OSD技术的应用范围非常广泛,尤其是在红外与电视多功能观瞄设备中,它是人机交互的桥。红外与电视多功能观瞄设备能够在全天候条件下观察目标,该设备工作在两种观测模式下都需要提供各种辅助信息以帮助观察者确定目标信息,这些辅助信息包括调节图像质量的莱单选项、瞄准目标的分划线,以及目标方位、距离信息等等。针对这个需求,本文在红外整机系统的基础上构建了OSD 系统。

对目前各种现存的OSD系统的实现方法进行了解后2-4,本文提出一种基于MCU+FPGA架构的共享缓存OSD系统的硬件设计与软件实现。

1OSD系统方案设计

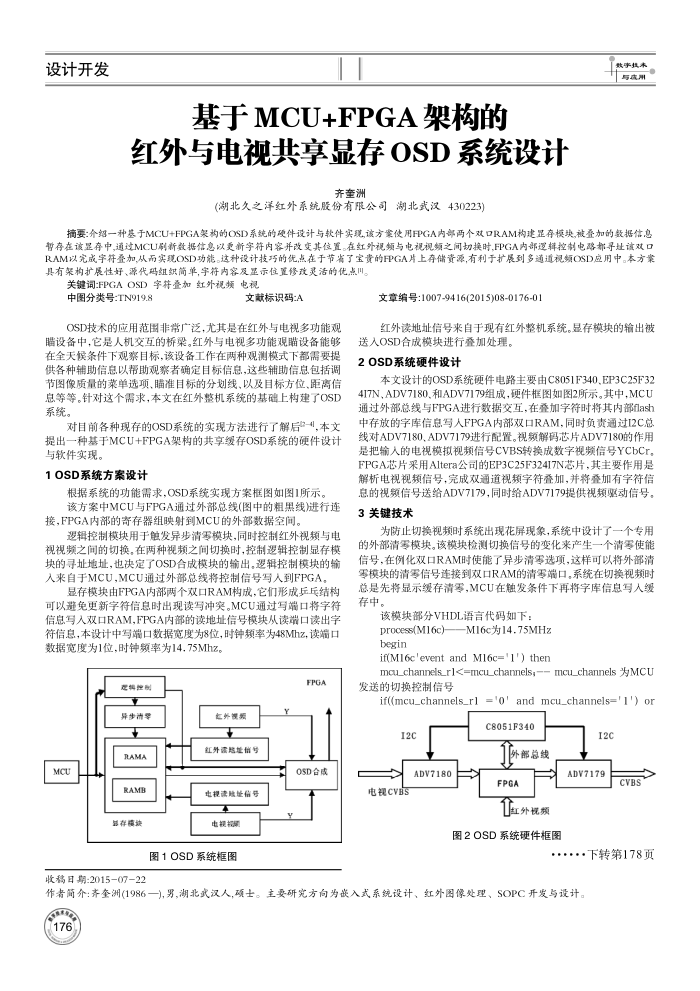

根据系统的功能需求,OSD系统实现方案框图如图1所示。该方案中MCU与FPGA通过外部总线(图中的粗黑线进行连

接,FPGA内部的寄存器组映射到MCU的外部数据空闻间

逻辑控制模块用于触发异步清零模块,同时控制红外视频与电视视频之间的切换。在两种视频之间切换时,控制逻辑控制显存模块的寻址地址,也决定了OSD合成模块的输出。逻辑控制模块的输入来自于MCU,MCU通过外部总线将控制信号写人到FPGA。

显存模块由FPGA内部两个双口RAM构成,它们形成乒乓结构可以避免更新字符信息时出现读写冲突。MCU通过写端口将字符信息写入双口RAM,FPGA内部的读地址信号模块从读端口读出字符信息,本设计中写端口数据宽度为8位,时钟频率为48Mhz,读端口数据宽度为1位,时钟频率为14.75Mhz。

FPGA

心转控

异步清车 LAM

MCU

RAME 品存覆块

收稿日期:20150722

在外规员

红外资路址册号

OSD合成

电规读联址信号电视损据

图1OSD系统框图

文章编号:1007-9416(2015)08-0176-01

红外读地址信号来自于现有红外整机系统。显存模块的输出被

送入OSD合成模块进行叠加处理。 2OSD系统硬件设计

本文设计的OSD系统硬件电路主要由C8051F340,EP3C25F32 417N,ADV7180.和ADV7179组成,硬件框图如图2所示。其中,MCU 通过外部总线与FPGA进行数据交互,在叠加字符时将其内部flash 中存放的字库信息写人FPGA内部双口RAM,同时负责通过I2C总线对ADV7180、ADV7179进行配置。视频解码芯片ADV7180的作用是把输人的电视模拟视频信号CVBS转换成数字视频信号YCbCr。 FPGA芯片采用AItera公司的EP3C25F32417N芯片,其主要作用是解析电视视频信号,完成双通道视频字符叠加,并将叠加有字符信息的视频信号送给ADV7179,同时给ADV7179提供视频驱动信号。 3关键技术

为防止切换视频时系统出现花屏现象,系统中设计了一个专用的外部清零模块。该模块检测切换信号的变化来产生一个清零使能信号,在例化双口RAM时使能了异步清零选项,这样可以将外部清零模块的清零信号连接到双口RAM的清零端口,系统在切换视频时总是先将显示缓存清零,MCU在触发条件下再将字库信息写人缓存中。

该模块部分VHDL语言代码如下:

prooess(M16c) begin

M16c为14.75MHz

if(M16c'event and M16c='1') then

mcu_channels_rl<=mcu_channels; mcu_channels 为MCU

发送的切换控制信号

and mcu_channels='') or

if(mcu_channels_rl

o

C8051F340

I2C

ADV7180

电视CVBS

外部总线 FPGA 缸外说频

图2OSD系统硬件框图

I2C

ADV7179

CVBS

..下转第178页

作者简介:齐奎洲(1986一),男,湖北武汉人,颈士。主要研究方向为嵌入式系统设计、红外图像处理、SOPC开发与设计。 176