基于Lagrange插值的数字重采样技术及FPGA实现

内容简介

我来与用

我来与用学术论坛

基于Lagrange插值的数字重采样技术

及FPGA实现

肖娜

(通信网信息传输与分发技术重点实验室河北石家庄050081)

摘要:数字重采样技术是数字信号处理领域研究的问题之一。利用数字重采样技术可以有效地实现任何采样率的变换。本文在讨论数字重采样原理的基础上,详细介绍了基于FPGA的软件端程技术实现基于Lagrange插值的数字重采样的基本原理和具体方法,并给出了相应的测试结果。

关键词:内插滤波器数字重采样立方Lagrange插值中图分类号:TN713

文献标识码:A

文章编号:1007-9416(2011)07-0193-02

在数字接收机设计领城里,常要求信号采样速率与符号速率成整数倍关系,以保证采样到最佳采样点。但在实际应用中信号采样速率和符号速率通常无法满足数倍关系,如果没有特殊处理,就不能提取到最佳采样点,从面降低解调性能。因此要求在处理中对信号先做一定预处理,即对信号进行数字重采样以改变信号采样速率,使其与符号速率满足整数借关系。

传统方法一般都是基于整数因子来实现整数倍或者分数倍的采样率变换的,若采样率的变换是整数倍,则只需通过抽取或内插就可以实现,若采样率的变换是分数倍,则一般是先内插后抽取来获得所要的采样率。这样做往往要内插几十倍基至上百倍,经过低通滤波器之后再进行几十倍的抽取,这不仅带来很大的运算量,而且当信号速率很高时,FPGA中很难稳定达到这么高的内插时钟,且低通滤波器又处在采样率最高的部分,这就给滤波器的设计带来了很高的难度。本文基于这个间题,提出一种利用插值滤波器的方

法实现信号的数字重采样,并给出了实现方案和测试结果。 1、数字重采样的原理

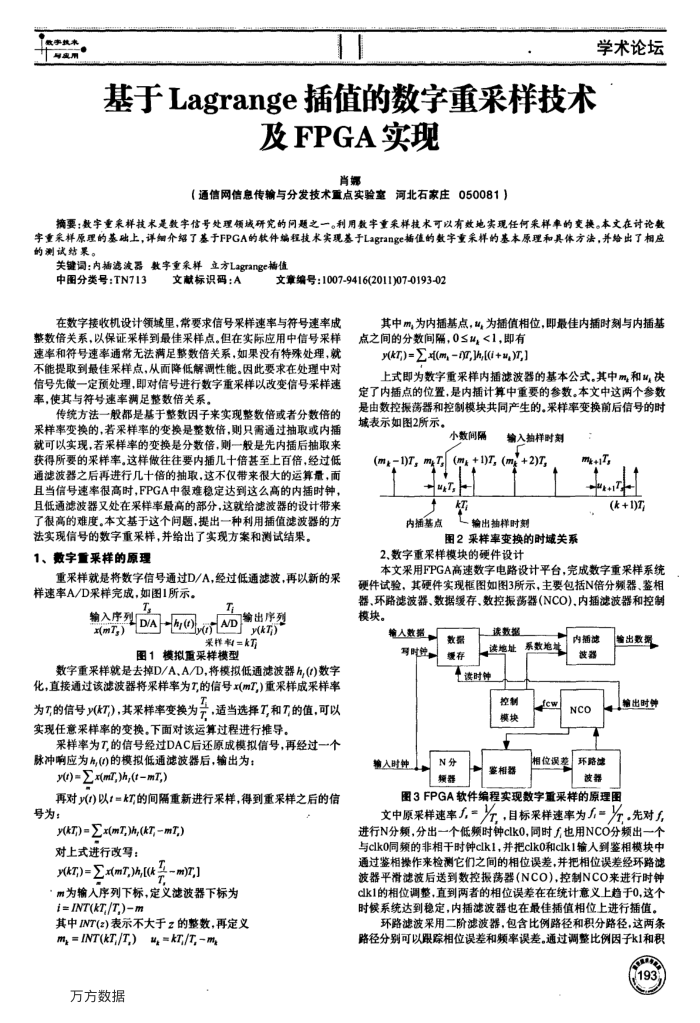

重采样就是将数字信号通过D/A,经过低通滤波,再以新的采样速率A/D采样完成,如图1所示。

AD输出序列

输入序列DA-

(mT,)

y(KT) 采样射二k万

图1模拟重采样模型

数字重采样就是去掉D/A.A/D,将模拟低通滤波器h,(0)数字化,直接通过该滤波器将采样率为工,的信号x(mT)重采样成采样率为,的信号(kT),其采样率变换为会,适当选择T,和T的值,可以实现任意采样率的变换。下面对该运算过程进行推导。

采样率为T,的信号经过DAC后还原成模拟信号,再经过一个脉冲响应为,(1)的模拟低通滤波器后,输出为:

y(t)=Zx(mT,)h,(t=mT,)

再对)以t=kT的间隔重新进行采样,得到重采样之后的信号为:

(KT) =x(mT,)h,(T, mT,) 对上式进行改写:

(KT)-Zx(mT,),[(-m)T,]

m为输入序列下标,定义滤波器下标为 i= INT(kT/T,)m

其中INT(2)表示不大于z的整数,再定义 m, = INT(KT,/T,)

),=T,/T,m

万方数据

其中m,为内插基点,",为插值相位,即最佳内插时刻与内插基点之间的分数间隔,0≤u,<1,即有

(KT,)=[(m, T,J,[(i+u,)T,)

上式即为数字重采样内插滤波器的基本公式其中m和,决定了内插点的位置,是内插计算中重要的参数。本文中这两个参数是由数控振荡器和控制模块共同产生的,采样率变换前后信号的时城表示如图2所示。

小数间隔

输入热样时刻

(m +1)T, (m,+2)T

(m,-1)T,m,T

+ 内插基点

T

输出热样时刻

图2采样率变换的时域关系

2、数字重采样模块的硬件设计

:

m+T, +11

(k+I)T

本文采用FPGA高速数字电路设计平台,完成数字重采样系统硬件试验,其硬件实现框图如图3所示,主要包括N倍分频器、鉴相器、环路滤波器、数据缓存、数控振荡器(NCO).内插滤波器和控制模块。

输入数措,写时丝。

输入时钟

数据缓存

读数据读地址

不读时钟

控制模块

N分

频预器

鉴相器

系数地址 few

内插滤波器

NCO

4

相位误差

蒙雄出波器

编出数况输出时停

图3FPGA软件编程实现数字重采样的原理图

,目标采样速率为.先对,

文中原采样速率J,

进行N分频,分出一个低频时钟clkO,同时J也用NCO分频出一个与clko同频的非相干时钟clk1,并把clko和clk1输人到鉴相模块中通过鉴相操作来检测它们之间的相位误差,并把相位误差经环路滤波器平滑滤波后送到数控振荡器(NCO),控制NCO来进行时钟 clk1的相位调整,直到两者的相位误差在在统计意义上趋于0,这个时候系统达到稳定,内插涉波器也在最佳插值相位上进行插值。

环路滤波采用二阶滤波器,包含比例路径和积分路径,这两条路径分别可以跟踪相位误差和频率误差。通过调整比例因子1和积

193