����ǰ��λ�ã���ҳ>��������>�߽�ɨ��ͻ�����ƽ���

�߽�ɨ��ͻ�����ƽ���

���ݼ��

ѧ����̳

ѧ����̳�߽�ɨ��ͻ�����ƽ���

��Ө1��ѩ��2���¡�������

(1.���Ǻ�������ְҵѧԺ��������572000��2.�������ӿƼ���ѧ��������71000��

4.���Ǻ�������ְҵѧԺ��������572000��4.�����ɻ����ʺ�������ɷ�����˾��������710089

��Ƥ

ժҪ�����Ļ����ֽε���ϵͳ���Եĸ���ߵıȽϣ�����չʾ����ɨ����Լ��������ƣ��ֱ��оƬ�ķ�չ����Ʒ������ڵ���������㷺Ӧ�����������������������ȫ����ͻ���˱߽�ɨè�����ƣ���Ϊ����ϵͳ������ڹ���ʦ�ṩ��ϵͳ����Ч�Ľ����

�ؼ������߽�ɨ�����IEEE1149���Ϸ�������ϵͳ��ͳ����

���ױ�ʶ�룺A

��ͼ����ţ�TH8

���±�ţ�1007-9416(2012)04-0270-02

�ֽ�ĵ�·��Խ��Խ�˸��ӣ���������Խ��Խ�ձ飬����ʹ�ø��ֱ���Ԫ����Ԫ�����Ĺܽźܽ��ܶȲ�����ߣ����� BGA��CSP,TCP��С�ķ�װ���Ա��ṩ��ǿ�Ĺ��ܣ���С���������ʡ�ɱ������Ӳ�Ʒ���ͻ�ʹ�ô�ͳ�������Ӵ��������ܽ��еIJ��Է��ʻ���Խ��Խ�٣����ô�ͳ��̽��������Ӵ���BGA��ijһ�Žţ�Ȼ������X���ߣ��������ܳ��ֺ���ľ�̬ͼ�������ṩȷ������������Ҫ�Ķ�̬�������棬��˺����ж��麸�Ϳɿ�����֮��IJ��졣

���룬�봲��X���߶���Ҫ�����ƽ̨����������������������߲�˵����������Ҳ����ӳ������������"ƿ��"��Ψһ;�����Ǽ�ǿ���������(DFT)���ڲ�Ʒ����ƽξͿ��Dz����ԣ�ͨ������һЩ����ĵ�·�ṹ�������ԭ��·�ڲ��ڵ�Ŀɿ��ԺͿɹ۲��ԣ��Ӷ�ʵ�ֶ��ڲ���·�IJ��ԡ�IEEE1149.1�������DZ߽�ɨ��ĵ�һ�������Ѿ������ֵ�·����õ��˹㷺��Ӧ�ã��� IEEE1149.4��ʹ�����ֺ�ģ���ϲ��Գ�Ϊ���ܣ�IEEE1149.5 ��ʵ���˲�����оƬ�����弶��ϵͳ���ķ�Ծ��IEEE1149.6�������˽������ͨ·�Ͳ��ͨ·�IJ��������������Ƴ���IEEE1149 7��Ѳ���Ŀ��������ܼ����ӵ�����ʽƬ��ϵͳ�ȡ������˱�

��ɨ����Լ����ڵ�������ȴ�ͳ�IJ���ƽ̨���������ơ� 1���߽�ɨ��ԭ��

IEEE1149.1���涨��һ�����ߴ��н��գ����������ǿ�ѡ�ģ����ýӿڳ������Էü�˿�(TAP)����ͼһ�����ڷ��ʸ��ӵļ��ɵ�·(IC)��������������DSP��ASIC��CPLD,����TAP֮�⣬���ICҲ������λ�Ĵ�����״̬������ִ�б߽�ɨ�蹦�ܣ���TDI(������������)���������˵�оƬ�е����ݴ洢��ָ��Ĵ����л�һ������������С��������ݴ�TDO(�����������)�������뿪оƬ���߽�ɨ������TCK������ʱ��)�ϵ��źż�ʱ������TMS(����ģʽѡ��)�ź�����TAP��������״̬��TRST(��������)��

Co

TDI

TOO

270

Cortrole

H

ͼһ�߽�ɨ�赥Ԫ����

Bendy ed on Banen

��ѡ�

��PCB�Ͽɴ��л�������ɼ���ɨ�蹦�ܵ�IC���γ�һ������ɨ������ͼ����ÿһ�������������ѵ�TAP��ÿһ��ɨ�����ṩ�����ü䣬�Ӵ���TAP�ӿڵ���Ϊ����һ���ֵ�ÿһ��IC�ϵ�ÿһ�����ߡ��������IJ��������У�ICִ����Ԥ�����ܣ��ͺ���߽�ɨ���·�����ڡ����ǣ���Ϊ�˽��в��Ի���ϵͳ��̶������豸��ɨ����ʱ�����ݿ��Դ��͵�IC�У�����ʹ�ô��нӿڴ�IC�ж�ȡ�������������ݿ������������豸���ģ����źŴ��豸���߷��͵� PCB�ϣ�����PCB���������߲������豸���

����֪����һ��IJ�Ʒ���������Ϊ����ƣ�����ԭ�ͣ���������Ʒ��������ά�ޣ���ͳ�������Ϊ������ԭ�ͳ����������صIJ��ԣ�����Ӳ�������ϵIJ��ԡ���ʵ�ϱ߽�ɨ����Լ�����������ƽν��в��ԣ�Ҳ����˵����������֣�PCBͼ����ʱ����ʵ�ֹ����Լ��ɲ��Եķ������Ӷ�����������ڼӿ�IJ�Ʒ����ʱ�䡣

Beundary Scan Nels

TAPF

TMS TCK

TOI

2�����Ϸ�������

TAP

ͼ�����JTAG����

TAP TDO

������ԭ����֪���߽�ɨ����Լ�����������²��ԣ�

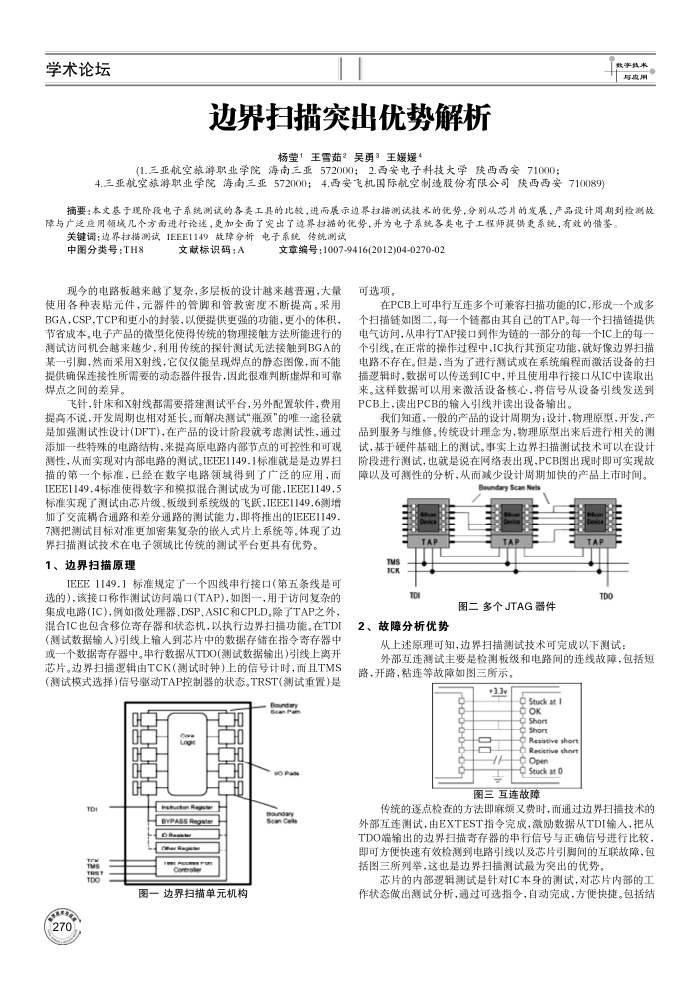

�ⲿ����������Ҫ�Ǽ��弶�͵�·������߹��ϣ�������·����·������ȹ�����ͼ����ʾ��

+3.3v

rO-0-0-0-0-0-6 P 0

�� Seuck at OK ��Short �� Short

Resistive sho O Retistive sho

Oper O Stuck at 0

ͼ����������

��ͳ�������ķ������鷳�ַ�ʱ����ͨ���߽�ɨ�輼�����ⲿ�������ԣ���EXTESTָ����ɣ��������ݴ�TDI���룬�Ѵ� TDO������ı߽�ɨ��Ĵ����Ĵ����ź�����ȷ�źŽ��бȽϣ����ɷ��������Ч����·�����Լ�оƬ���ż�Ļ������ϣ�����ͼ�����о٣���Ҳ�DZ߽�ɨ�������Ϊͻ�������ơ�

оƬ���ڲ������������IC�����IJ��ԣ���оƬ�ڲ��Ĺ���״̬�������Է�����ͨ����ѡָ��Զ���ɣ������ݡ�������

��һ�£����ñ䲽��NLMS�㷨�Ļ�������ϵͳ

��һ�£�ۻ��˫���ߵĿ����ż�������ԭ��