您当前的位置:首页>论文资料>超声波流量计的FPGA测试与仿真

内容简介

数字技术与应用

数字技术与应用超声波流量计的FPGA测试与仿真

聚明夏书峰

(大连理工大学

杨国涛

辽宁大速

于泽 116024)

理论探索:

搞要,在SOPC(SystemOnProgrammableChip)技术的基础上,针对交叉产路时差法注量计,设计了一款基于FPGA拉术的电路系镜据速了所设计的电路系统的短成,给出了IP模块ModelSim仿具测试波形。

关键调:可端程片上系统

可端桂还辑降列如识产权核

中图分类号:TH702 1引言

文献标识码;A

文章编号:1007-9416(2010)08-0182-02

MicroBlaze及大量的IP,设计成能够完成数

超声波流量计利用流体对超声波信号的调制作用,通过检测信号的变化来获得体积流量"。

所着大规模集成电路技术的飞速发展,及流体的层流状态与絮流状态流速分布规律的理论分析,超声波流量计的测量精度得以进一步的提高[2],

本文尝试利用SOPC技术实现流量计电路系统,这种设计有利于提高测量精度,便于系统升级。

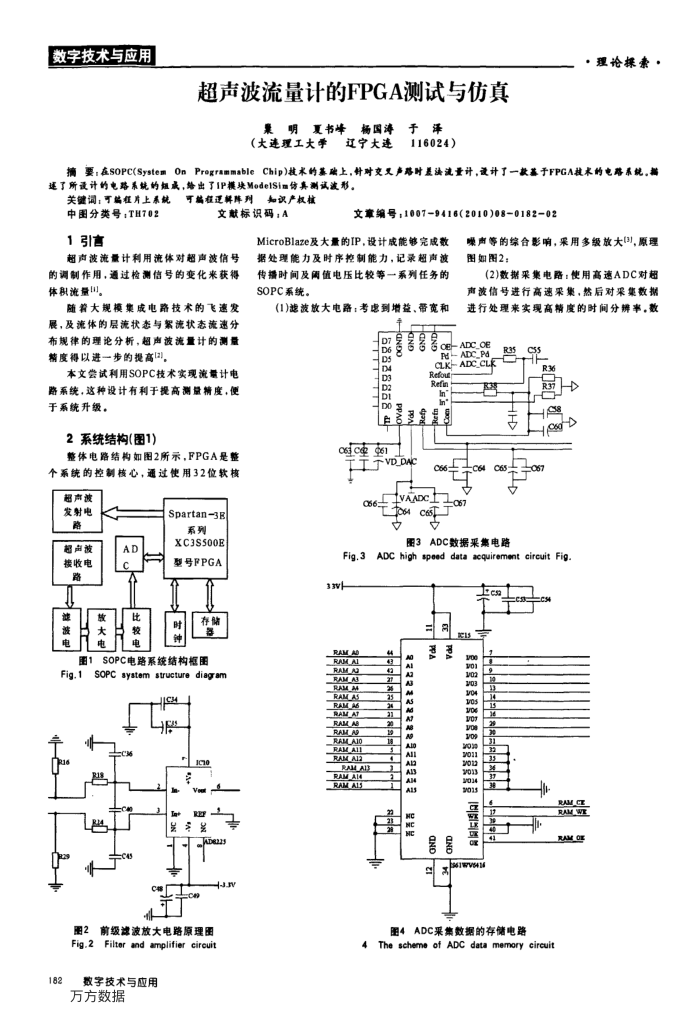

2系统结构(图1)

整体电路结构如图2所示,FPGA是整个系统的控制核心,通过使用32位软核

超声波

发射电路

超声被接收电

游波电

电

AD 较

Spartan-38 系列

XC3S500E 号PPGA

时

存储

SOPC电路系统结构框图图1

Fig.1 R29

SOPC system structure diagam

IC4

e REF

Te

C

Ae22

H-.

09

图2

前级滤波放大电路原理图 Filter and amplifier cirouit

Fig.2

182

数字技术与应用万方数据

据处理能力及时序控制能力,记录超声波传播时间及阔值电压比较等一系列任务的 SOPC系统。

(1)慈波效大电路:考虑到增益、带宽和

噪声等的综合影响,采用多级放大(3],原理图如图2:

(2)数据采集电路:使用高速ADC对超声波信号进行高速采集,然后对采集数据进行处理来实现高精度的时间分辨率,数

ADC.OE

Ce

PACP

CLKh Refout Refin

pe

e

1

专

vpDae

ADC_CLK

R35 全

C65

C64

文

067

c

文

全

sso R36 Y 2067

ADC数据采集电路图3

ADC high speed data acquirement circuit Fig.

Fig.3 33vh

63

PPA

RAMA RAM_A AMA

A A RAMAS RAHA AM_A AMAI CAL RAMLAI RAMAIA

30 23

222 M AS 心心皇

QNO

OND

y0e 营营营查管管管营营委#婴婴装 os 国al

1361WV5416

G

RALCE RAM_WT

RAMKOE

图4ADC采集数据的存储电路

The scheme of ADC data memory circuit

4

上一章:财税库行信息系统安全方案设计

下一章:财经新闻挖掘系统中特征选择算法研究