����ǰ��λ�ã���ҳ>��������>����������ӦRS-485�м��������

����������ӦRS-485�м��������

���������������

�ĵ���ʽ��PDF���Ӱ�

�ļ���С��1006.63 KB

�������ԣ�����

����ʱ�䣺2024-11-29 17:47:40

���ݼ��

����������ӦRS-485�м��������

����������ӦRS-485�м���������ܵ¾�

���иּ�������ɽ��ɽ�о�Ժ����˾��������ɽ243000)

��ƿ���

ժҪ:RS4-85ͨѶ�ڹ�ҵ���Ƽ��Զ����DZ��б��㷺���ã������е�·�ṹ������������ǿ���������Զ���ص㡣RS-485��������ֻ���������ͽ��в���,���粻�ܳ��ַ�֧����˶�ʵ�ʲ�����Ƽ�ʩ����ɺܴ��Ѷȡ����Ľ�����һ���������ӦRS-485�����м�����·���õ�·����ʵ�����߸��롢��֧����չ�ȹ��ܣ���Ч�����˵�·���˽ṹ����߿ɿ��Լ���Ӧ������Ϊ����ʩ�����������ʹ����

�ؼ�����SP485�ӿ�оƬ�������������ӿ����

��ͼ����ţ�TP273

���ױ�ʶ��:A

RS-485�����ɵ��ӹ�ҵЭ��(EIA)��ͨѶ��ҵЭ��(TIA)������ҵЭ�Ṳͬ�������ƶ��ġ�RS-485������Ϊһ�ֶ�������ݴ���ĵ����淶�棬�ѳ�Ϊҵ��Ӧ����Ϊ�㷺�ı�ͨ�Žӿ�֮��485ͨ�Žӿ�������һ��˫������ʵ�����ӽṹ�Ķ��˫��ͨ�ţ���һ����վ�����ڸ���վ�����е������������������ݴ������ʡ��绺���ȼ��ɿ�����������������ġ���ˣ�������Ƕ�����RSһ485��Ϊ���ݴ�����·���繤ҵ���ơ������DZ�������¥�ֵȡ� RS-485.���߲����ն�ƥ��������ͽṹ���˽ṹ����һ��������ͨѶ���߽������ڵ㴮�������������ϵ�ÿ�������ڵ��֧���³���Ӧ�����ܵ����̣��Խ��ͷ�֧���µķ����źŶ����ߵ�Ӱ�졣����485��֧�����Խ��������ӱ�Ϊ�������ӣ�������֧�����źŷ�������ߵ�Ӱ�죬�Ż����������˽ṹ

����֧����·��Ҫ��485�ӿ�оƬ���������ͨ��·�������

Դ����ص�����Ԫ�����ɡ��õ�·�����Զ�ʶ���л����������������Զ���Ӧ���߲����ʵı仯��ͬʱ�����е�������ͷ���

RO h 2 DE3 DI

SP485

ͼ1SP485оƬ��������

R ONDI

R12

TDLTU

OND

GRDt

�ո����ڣ�2016-04-20

OND Vcc R4

DE

GNDI

Vco GND

2 U3

C1:

ND

���±�ţ�1007-9416(2016)07-0179-01 ��ӿ�Ĺ��ܡ�

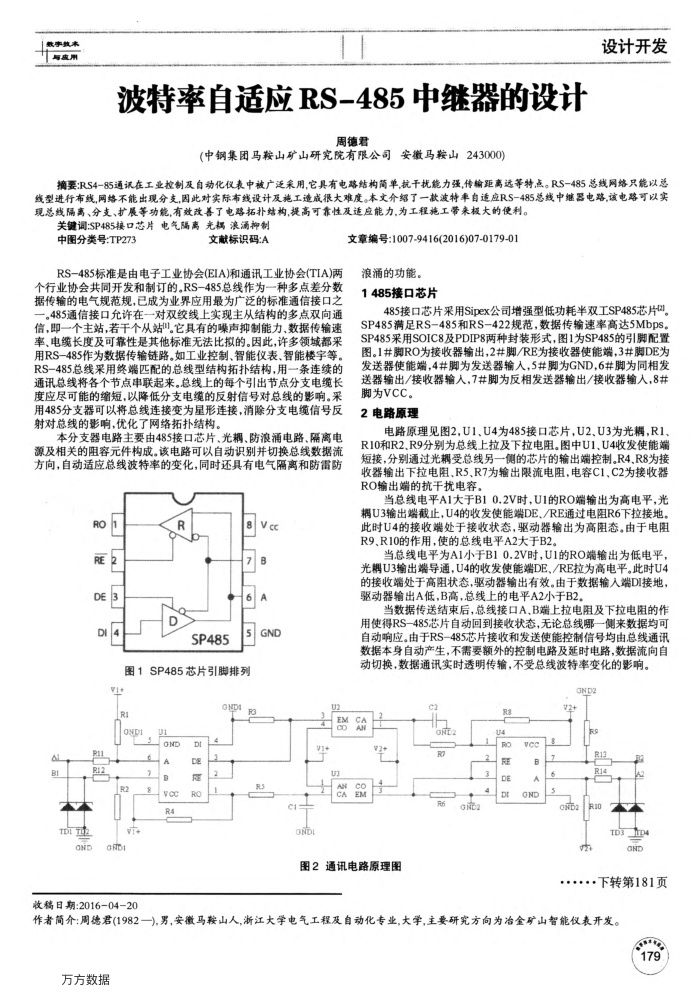

1485�ӿ�оƬ

485�ӿ�оƬ����Sipex��˾��ǿ�͵��İ�˫��SP485оƬ SP485����RS-485��RS-422�淶�����ݴ������ʸߴ�5Mbps SP485����SOIC8��PDIP8���ַ�װ��ʽ��ͼ1ΪSP485����������ͼ��1#��ROΪ�����������2#��/REΪ������ʹ�ܶˣ�3#��DEΪ������ʹ�ܶˣ�4#��Ϊ���������ˣ�5����ΪGND.6��Ϊͬ��������/���������ˣ�7#��Ϊ����������/���������룬8#

��ΪVcc�� 2��·ԭ��

��·ԭ����ͼ2��U1��U4Ϊ485�ӿ�оƬ��U2��U3Ϊ���R1 R10��R2��R9�ֱ�Ϊ�����������������衣ͼ��U1��U4�շ�ʹ�ܶ˶̽ӣ��ֱ�ͨ��������������һ���оƬ������˿��ơ�R4R8Ϊ����������������衢R5��R7Ϊ����������裬����C1��C2Ϊ������ RO����˵Ŀ����ŵ��ݡ�

�����ߵ�ƽA1����B10.2Vʱ��U1��RO�����Ϊ�ߵ�ƽ������U3����˽�ֹ��U4���շ�ʹ�ܶ�DE��/REͨ������R6�����ӵش�ʱU4�Ľ��ն˴��ڽ���״̬�����������Ϊ����̬�����ڵ��� R9,R10�����ã�ʹ�����ߵ�ƽA2����B2��

�����ߵ�ƽΪA1С��B10.2Vʱ��U1��RO�����Ϊ�͵�ƽ��

����U3����˵�ͨ��U4���շ�ʹ�ܶ�DE��/RE��Ϊ�ߵ�ƽ����ʱU4 �Ľ��ն˴��ڸ���״̬�������������Ч���������������DI�ӵأ����������A�ͣ�B�ߣ������ϵĵ�ƽA2С��B2��

�����ݴ��ͽ��������߽ӿ�A��B���������輰�������������ʹ��RS-485оƬ�Զ��ص�����״̬������������һ�������ݾ����Զ���Ӧ������RS-485оƬ���պͷ���ʹ�ܿ����źž�������ͨѶ���ݱ����Զ�����������Ҫ����Ŀ��Ƶ�·����ʱ��·�����������Զ��л�������ͨѶʵʱ�����䣬�������߲����ʱ仯��Ӱ�졣

OND2

R8

ont R7

ͼ2ͨѶ��·ԭ��ͼ

G2

U4

GN

+

R13 R14

oND2

ID3

GND

.��ת��181ҳ

����飺�ܵ¾�(1982һ)�У���������ɽ��,�㽭��ѧ�������̼��Զ���רҵ����ѧ����Ҫ�о�����Ϊұ���ɽ�����DZ�������

179

������

��һ�£�sipЭ�����������е�Ӧ��

��һ�£�SF6ˮ�M�ܶ�����ʽ���װ�õ��о�