您当前的位置:首页>论文资料>并行机中的Cache一致性技术研究

内容简介

・应用技术・

・应用技术・并行机中的Cache一致性技术研究

张扬奇

肖学福

(总后军事交通运输研究所

高兵权刘金彪

天津河东

300161)

数字技术与应用

[摘要]随着信息技术的发展,并行处理变得越来越普遍,本文在分析并行处理共享存储器特点的基确上,设计了一种树形COMA 并行机结构,并对Cache一致性进行了研究。

[关键词]并行机Cache[中图分类号]T

一致性

[文献标识码]A

[文章编号]10079416(2010)030093-02

[Abstract)This paper analyzes the basic characteristics of shared memory in the multiprocessor multi-memory parallel machine System, designs a parallel computer architecture named treebased COMA (Cache Only Memory Access)type.

[Key Words]Parallel Machine Cache Consistence

研究背景 1

多处理器(P)多存储器(M)的系统中,多M共享,有三种方案,分别是UMA, NUMA和NORA,UMA并行机,存储器M 和公共信息传输通道IN的结构与冯诺依受体系结构基本一致,M采用统一地址编址。而P的个数由1个增加到多个。P通过竞争使用IN,并采用统一地址访间M。

软件设计上,UMA并行机软件与冯诺依受结构也非常相似。

UMA并行机通过

定措施,使多个P模拟为一个性能强大的 P,从面使得基于冯诺依曼系统开发的程序经过很少的改造,就可运行在UMA并行机上。但是,随差P和M数目的增多,处理器冲突频策,IN争用间题严重,限制了 UMA并行机规模,

在大规模并行机中,P与M结合方式需重新设计,出现了NUMA并行机系统结

M Pr

(P2)

M

图1UMA并行机系统结构

CD,3

构,见图2。NUMA机中M仍然统一编址,但P是非均一性的。从访间速度上来看,P 访间临近的M速度快,从访间冲突来看, P访间临近的M不会干涉其它访存操作,与UMA并行机相比,NUMA机中P对IN 的访间频率降低,系统并行规模可大大提高,

按照高速缓存Cache、存储器M与信道 IN结合方式不同,可将NUMA并行机分为CC-NUMA并行机和COMA并行机,本文将差重分析COMA并行机。

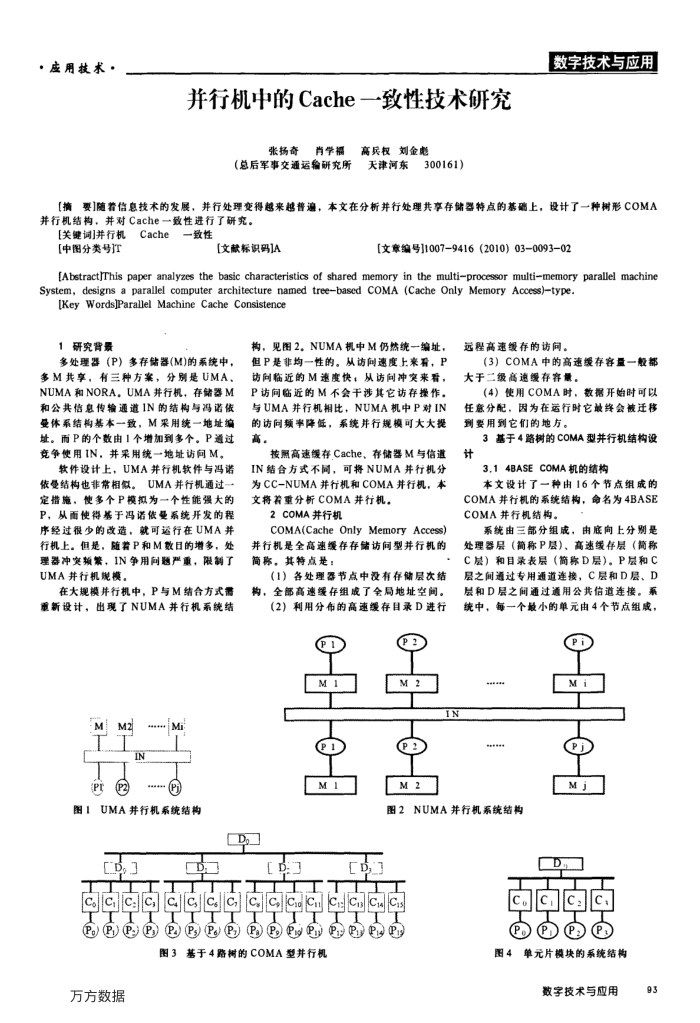

2COMA并行机

COMA(Cache Only Memory Access) 并行机是全高速缓存存储访间型并行机的简称,其特点是:

(1)各处理器节点中没有存储层次结构,全部高速缓存组成了全局地址空间。

(2)利用分布的高速缓存目录D进行

D

M1 M1

L

M2

IN

@ M2

远程高速缓存的访间。

(3)COMA中的高速缓存容量一般部大于二级高速缓存容量。

(4)使用COMA时,数据开始时可以任意分配,因为在运行时它最终会被迁移到要用到它们的地方。

3基于4路树的COMA型并行机结构设

计

3.14BASECOMA机的结构

本文设计了一种由16个节点组成的

COMA并行机的系统结构,命名为4BASE COMA并行机结构。

系统由三部分组成,由底向上分期是处理器层(简称P层)、高速线存层(简称 C层)和目录表层(简称D层)。P层和C 层之间通过专用通道连接,C层和D层、D 层和D层之闻通过通用公共信道连接。系统中,每一个般小的单元由4个节点组成,

P Mi

Mj

图2NUMA并行机系统结构

D.

电

@@@

图3基于4路树的COMA型并行机

万方数据

eee 图4单元片模块的系统结构

数字技术与应用

6

上一章:表格与DIV+CSS的布局设计分析

下一章:PLM系统在产品档案管理中的应用