您当前的位置:首页>论文资料>数字阵列雷达系统的 BIT 设计

内容简介

设计开发

设计开发数字阵列雷达系统的BIT设计

黄正英

(中国电子科技集团公司第三十八研究所安徽合肥230031)

与皮

摘要:随着现代电子技水的发展,数宇阵列雷达已从概念、关键技术研究、实验系统研究转到工程化实用化阶投。同时数字阵列雷达的高集成度给测试和维修带来一定的难度,本文结合某型数字降列雷达的测试性设计,给出了一个典型的数字阵列雷达BIT设计方案,该方案在实际运用中获得了较好的评价。

关键调:数宇阵列需达加电BIT周期BIT炸护BIT 中图分类号:TN957.51

文献标识码:A

1、引言

文章编号:1007-9416(2012)05-0124-02

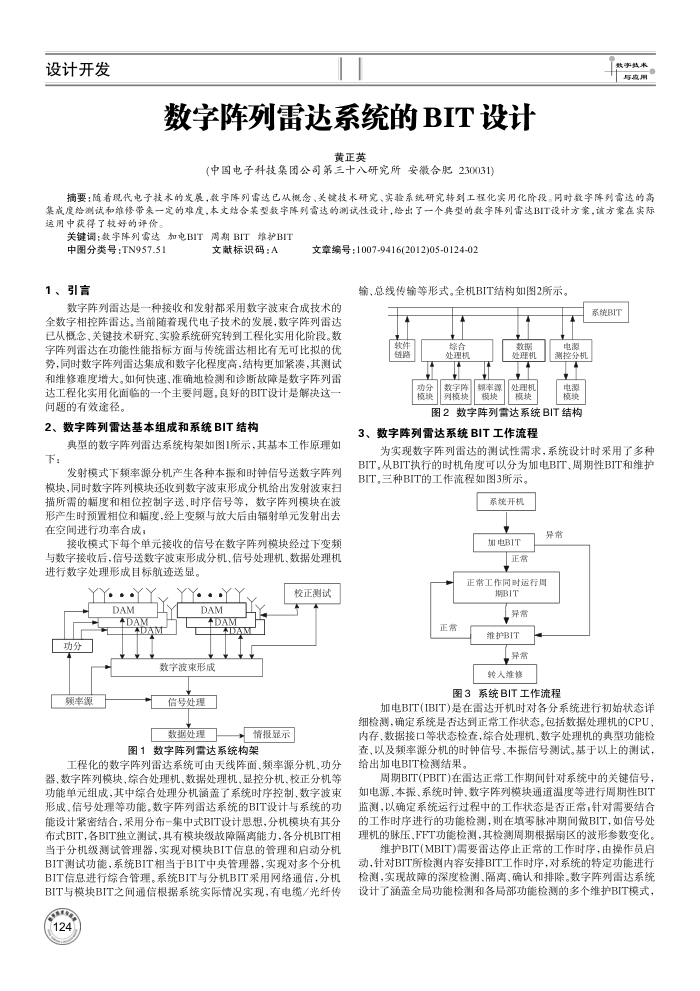

输,总线传输等形式。全机BIT结构如图2所示。

数字阵列雷达是一种接收和发射都采用数字波束合成技术的全数字相控阵雷达,当前随着现代电子技术的发展,数字阵列雷达已从概念、关键技术研究、实验系统研究转到工程化实用化阶段。数字阵列雷达在功能性能指标方面与传统雷达相比有无可比拟的优势,同时数字阵列雷达集成和数字化程度高,结构更加紧凑,其测试和维修难度增大。如何快速,准确地检测和诊断故障是数字阵列雷达工程化实用化面临的一个主要间题。良好的BIT设计是解决这一问题的有效途径。

2、数字阵列雷达基本组成和系统BIT结构

典型的数字阵列雷达系统构架如图1所示,其基本工作原理如下:

发射模式下频率源分机产生各种本振和时钟信号送数字阵列模块,同时数字阵列模块还收到数字波束形成分机给出发射波束扫描所需的幅度和相位控制字送、时序信号等,数字阵列模块在波形产生时预置相位和幅度,经上变频与放大后由辐射单元发射出去在空间进行功率合成

接收模式下每个单元接收的信号在数字阵列模块经过下变频与数字接收后,信号送数字波束形成分机、信号处理机、数据处理机进行数字处理形成目标航迹送显。

YY...Y

DAM 4DAM

A

功分

Y...YY

DAM

DAM

数字波束形成

额率源

信号处理

数据处理

校正测试

情报显示

图1数字阵列需达系统构架

工程化的数字阵列雷达系统可由天线阵面、频率源分机,功分器、数字阵列模块、综合处理机、数据处理机、显控分机、校正分机等功能单元组成,其中综合处理分机通盖了系统时序控制、数字波束形成、信号处理等功能。数字阵列雷达系统的BIT设计与系统的功能设计紧密结合,采用分布一集中式BIT设计思想,分机模块有其分布式BIT,各BIT独立测试,具有模块级故障隔离能力,各分机BIT相当于分机级测试管理器,实现对模块BIT信息的管理和启动分机 BIT测试功能,系统BIT相当于BIT中央管理器,实现对多个分机 BIT信息进行综合管理。系统BIT与分机BIT采用网络通信,分机 BIT与模块BIT之间通信根据系统实际情况实现,有电缆/光纤传

软件魏路

综合处理机

功分数字陈模块

列模块

数据处理机

处理机

频率源

模块

模块

电源测控分机

电源模块

图2数字阵列需达系统BIT结构

3、数字阵列雷达系统BIT工作流程

系统BIT

为实现数字阵列雷达的测试性需求,系统设计时采用了多种 BIT。从BIT执行的时机角度可以分为加电BIT、周期性BIT和维护 BIT,三种BIT的工作流程如图3所示。

系烷开机

加电BIT

正常

异常

正常工作同时运行周

期BIT

正需

「异常维护BIT 异常较人维修

图3系统BIT工作流程

加电BIT(IBIT)是在雷达开机时对各分系统进行初始状态详细检测,确定系统是否达到正常工作状态。包括数据处理机的CPU,内存、数据接口等状态检查,综合处理机、数字处理机的典型功能检查,以及频率源分机的时钟信号、本振信号测试。基于以上的测试,给出加电BIT检测结果。

周期BIT(PBIT)在雷达正常工作期间针对系统中的关键信号,如电源、本振、系统时钟、数字阵列模块通道温度等进行周期性BIT 监测,以确定系统运行过程中的工作状态是否正常,针对需要结合的工作时序进行的功能检测,则在填零脉冲期间做BIT,如信号处理机的脉压,FFT功能检测,其检测周期根据扇区的波形参数变化。

维护BIT(MBIT)需要雷达停止正常的工作时序,由操作员启动,针对BIT所检测内容安排BIT工作时序,对系统的特定功能进行检测,实现故障的深度检测、隔离、确认和排除。数字阵列雷达系统设计了涵盖全局功能检测和各局部功能检测的多个维护BIT模式,