您当前的位置:首页>论文资料>雷达数字插件测试台下位机设计

内容简介

数事我术与高用

数事我术与高用雷达数字插件测试台下位机设计

伍云辉刘娟沈光正

(华东电子工程研究所安徽合肥230031)

设计开发

摘要为了实现雷达数字拖件的自动测试提出了一种由上佳机、下佳机和测试背板组成的测试台系统设计方案详细介结了该系统中下位机的硬件及软件设计。该下位机硬件主要以丧入式计算机模块为核心,软件主要实现通讯控制,自检测试,通试测试库和故障诊断床等模块的功能。实践表明,该下位机能稳定有效地完成自动测试各项功能。

关键词:雷达数字循件测试台下位机故障测试

中图分类号:TP306 1系统设计方案

文献标识码:A

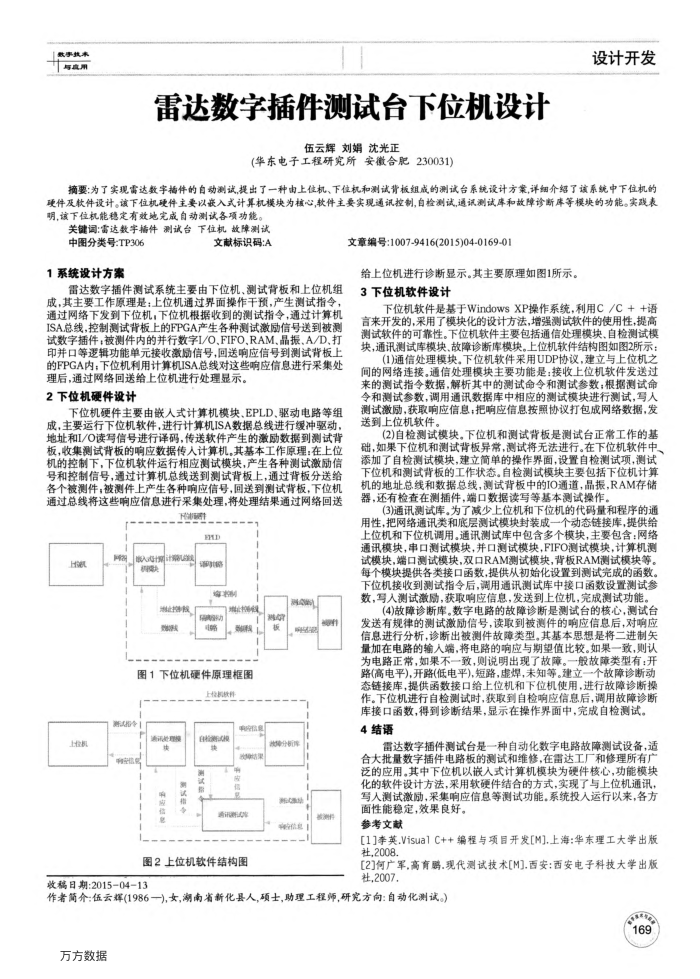

雷达数字插件测试系统主要由下位机、测试背板和上位机组成,其主要工作原理是:上位机通过界面操作干预,产生测试指令,通过网络下发到下位机,下位机根据收到的测试指令,通过计算机 ISA总线,控制测试背板上的FPGA产生各种测试激励信号送到被测试数字插件:被测件内的并行数字I/OFIFO,RAM、晶振,A/D,打印并口等逻辑功能单元接收激励信号,回送响应信号到测试背板上的FPGA内;下位机利用计算机ISA总线对这些响应信息进行采集处

理后,通过网络回送给上位机进行处理显示。 2下位机硬件设计

下位机硬件主要由嵌人式计算机模块、EPLD、驱动电路等组成,主要运行下位机软件,进行计算机ISA数据总线进行缓冲驱动,地址和I/O读写信号进行译码,传送软件产生的激励数据到测试背板,收集测试背板的响应数据传人计算机。其基本工作原理:在上位机的控制下,下位机软件运行相应测试模块,产生各种测试激励信号和控制信号,通过计算机总线送到测试背板上,通过背板分送给各个被测件,被测件上产生各种响应信号,回送到测试背板,下位机通过总线将这些响应信息进行采集处理,将处理结果通过网络回送

E

Het

海

6

避

808

我

图1下位机硬件原理框图

上控款用

指

通

机

空信务

自

Re 结果

信品通

图2上位机软件结构图

收稿日期:2015-0413

板

我分牌

30

se

文章编号:1007-9416(2015)04-0169-01

给上位机进行诊断显示。其主要原理如图1所示。 3下位机软件设计

下位机软件是基于WindowsXP操作系统,利用C/C++语言来开发的,采用了模块化的设计方法,增强测试软件的使用性,提高测试软件的可靠性。下位机软件主要包括通信处理模块、自检测试模块,通讯测试库模块、故障诊断库模块。上位机软件结构图如图2所示:

(1)通信处理模块。下位机软件采用UDP协议,建立与上位机之间的网络连接。通信处理模块主要功能是:接收上位机软件发送过来的测试指令数据,解析其中的测试命令和测试参数:根据测试命令和测试参数,调用通讯数据库中相应的测试模块进行测试,写人测试激励,获取响应信息;把响应信息按照协议打包成网络数据,发送到上位机软件。

(2)自检测试模块。下位机和测试背板是测试台正常工作的基础,如果下位机和测试背板异常,测试将无法进行。在下位机软件中添加了自检测试模块,建立简单的操作界面,设置自检测试项,测试下位机和测试背板的工作状态。自检测试模块主要包括下位机计算机的地址总线和数据总线,测试背板中的IO通道,晶振,RAM存储器,还有检查在测插件,端口数据读写等基本测试操作。

(3)通讯测试库。为了减少上位机和下位机的代码量和程序的通用性,把网络通讯类和底层测试模块封装成一个动态链接库,提供给上位机和下位机调用。通讯测试库中包含多个模块,主要包含:网络通讯模块,串口测试模块,并口测试模块,FIFO测试模块,计算机测试模块,端口测试模块,双口RAM测试模块,背板RAM测试模块等。每个模块提供各类接口函数,提供从初始化设置到测试完成的函数。下位机接收到测试指令后,调用通讯测试库中接口函数设置测试参数,写人测试激励,获取响应信息,发送到上位机,完成测试功能。

(4)故障诊断库。数字电路的故障诊断是测试台的核心,测试台发送有规律的测试激励信号,读取到被测件的响应信息后,对响应信息进行分析,诊断出被测件故障类型。其基本思想是将二进制失量加在电路的输人端,将电路的响应与期望值比较。如果一致,则认为电路正常,如果不一致,则说明出现了故障。一般故障类型有:开路(高电平),开路(低电平)短路,虚焊,未知等。建立一个故障诊断动态链接库,提供函数接口给上位机和下位机使用,进行故障诊断操作。下位机进行自检测试时,获取到自检响应信息后,调用故障诊断库接口函数,得到诊断结果,显示在操作界面中,完成自检测试。

4结语

雷达数字插件测试台是一种自动化数字电路故障测试设备,适合大批量数字插件电路板的测试和维修,在雷达工厂和修理所有广泛的应用。其中下位机以嵌入式计算机模块为硬件核心,功能模块化的软件设计方法,采用软硬件结合的方式,实现了与上位机通讯写人测试激励,采集响应信息等测试功能。系统投入运行以来,各方

面性能稳定,效果良好。参考文献

[1]李英.Visua1C++编程与项目开发[M].上海:华东理工大学出版社,2008

[2]何广军,高育鹏.现代测试技术[M].西安:西安电子科技大学出版社,2007

作者简介:伍云辉(1986一),女,潮南省新化县人,硕士,助理工程师,研究方向:自动化测试。)

169

万方数据