基于BU-61580的航空1553B总线RT模式设计

内容简介

应用研究

应用研究数学数来与成用

基于BU-61580的航空1553B总线RT模式设计

杨旭黄建国杨尚明李力

(电子科技大学四川成都611700)

摘要:BU-61580是航空工程领成广流采用的MIL-STD-1553B总线的控制芯片,本文从硬件连接,逻辑时序以及软件设计三方面论述了 BU-61580工作于RT模式时的系统设计方案。硬件基于FPGA与DSP实现,增强了整个系统的可载劳性与移植性。

关键调:1553B总线BU61580RT模式TMS320F2812EP2C20 中图分类号:TP336

文章编号:1007-9416(2012)01-0060-03

文献标识码:A

1、引言

BU-61580是美国DDC公司设计的MIL-STD-1553B总线控制芯片,其集1553B总线协议的BC/RT/MT模式与一身,具有双收发器模块、协议处理器部件,存储器管理部件以及与不同微处理器的逻辑接口,内部还集成了一个4K字节的共享RAM。对1553B总线的全协议支持以及灵活的使用方式,使得BU-61580在航空工程领域占领了很大的市场份额。本次设计在硬件上将BU-61580与FPGA 和DSP结合使用,这样在不更改硬件连接的前提下,可以方便的将整个系统移植于BC/RT/MT三种不同的应用系统中。本文以RT模式为重点,论述在该应用方式下BU-61580芯片的硬件连接方式与软件设计实现。

硬件系统设计 2、

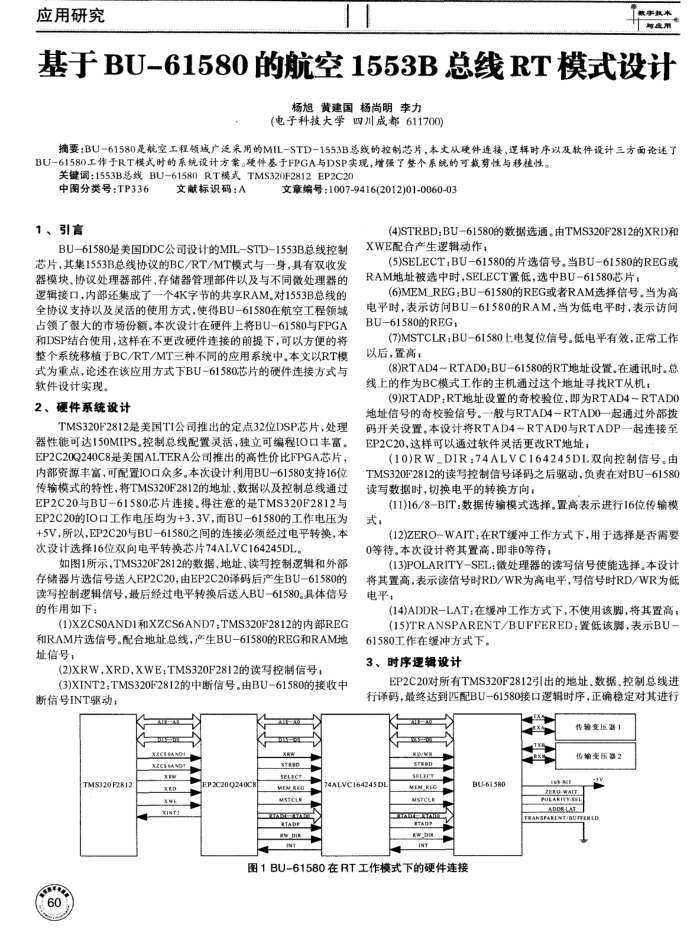

TMS320F2812是美国TI公司推出的定点32位DSP芯片,处理器性能可达150MIPS。控制总线配置灵活,独立可编程IO口丰富。 EP2C20Q240C8是美国ALTERA公司推出的高性价比FPGA芯片,内部资源丰富,可配置1O口众多。本次设计利用BU-61580支持16位传输模式的特性,将TMS320F2812的地址、数据以及控制总线通过 EP2C20与BU-61580芯片连接。得注意的是TMS320F2812与 EP2C20的IO口工作电压均为+3.3V,而BU-61580的工作电压为 +5V,所以,EP2C20与BU-61580之间的连接必须经过电平转换,本次设计选择16位双向电平转换芯片74ALVC164245DL。

如图1所示,TMS320F2812的数据,地址、读写控制逻辑和外部存储器片选信号送入EP2C20,由EP2C20译泽码后产生BU一61580的读写控制逻辑信号,最后经过电平转换后送人BU一61580。体信号的作用如下:

(1)XZCS0AND1和XZCS6AND7:TMS320F2812的内部REG 和RAM片选信号。配合地址总线,产生BU-61580的REG和RAM地址信号:

(2)XRW,XRD,XWE:TMS320F2812的读写控制信号,

(3)XINT2:TMS320F2812的中断信号。由BU-61580的接收中断信号INT驱动;

XRW

XZCS 6A NDT

TMS320F2812

XRD XE XINT2

60

EP3C20Q240C

STRBD SELECr MEM.REG MSTCLR

AEY RTADF m

(4)STRBD:BU-61580的数据选通,由TMS320F2812的XRD和 XWE配合产生逻辑动作:

(5)SELECT:BU-61580的片选信号。当BU-61580的REG或 RAM地址被选中时,SELECT置低,选中BU-61580芯片:

(6)MEM_REG:BU-61580的REG或者RAM选择信号,当为高电平时表示访问BU-61580的RAM,当为低电平时,表示访间 BU61580的REG;

(7)MSTCLR:BU-61580上电复位信号。低电平有效,正常工作以后,置高;

(8)RTAD4RTAD0;BU-61580的RT地址设置。在通讯时,总线上的作为BC模式工作的主机通过这个地址寻找RT从机:

(9)RTADP:RT地址设置的奇校验位,即为RTAD4~RTAD0 地址信号的奇校验信号。-般与RTAD4~RTADO一起通过外部拨码开关设置。本设计将RTAD4~RTAD0与RTADP一起连接至 EP2C20,这样可以通过软件灵活更改RT地址;

(10)RW_DIR:74ALVC164245DL双向控制信号。由 TMS320F2812的读写控制信号译码之后驱动,负责在对BU-61580 读写数据时,切换电平的转换方向

(11)16/8-BIT:数据传输模式选择。置高表示进行16位传输模式,

(12)ZERO-WAIT:在RT缓冲工作方式下,用于选择是否需要 0等待。本次设计将其置高,即非0等待,

(13)POLARITY-SEL:微处理器的读写信号使能选择。本设计将其置高,表示读信号时RD/WR为高电平,写信号时RD/WR为低电平:

(14)ADDR-LAT:在缓冲工作方式下,不使用该脚,将其置高;(15TRANSPARENT/BUFFERED:置低该脚.表示BU-

61580工作在缓冲方式下。

时序逻辑设计 3、

EP2C20对所有TMS320F2812引出的地址、数据、控制总线进行译码,最终达到匹配BU-61580接口逻辑时序,正确稳定对其进行

传输变压器1

/ STRBI SELECT MEM.REG 131R

ETADP ww_D IN

V

图1BU-61580在RT工作模式下的硬件连接

BU-61580

ZERO-WA

传编变器2

ADT TRANSPARENT/BUTTERED