基于泰勒级数展开法的DSP正弦信号发生器设计

内容简介

数学热本与表用

数学热本与表用设计开发

基于泰勒级数展开法的DSP正弦信号发生器设计

姜志鹏1程嫂嫂2

(1.金陵科技学院信息技术学院,南京国际软件学院江苏南京211169

2.江苏师范大学物理与电子工程学院江苏徐州221116)

摘要:泰物级数是使用多项式通近已知函数的常用方法,本文分析了正张信号的泰独级数展开算法基于TI公司C54xx系列DSP芯片的汇端语言编程实现该算法,并使用了存储单元复用的方法解决了为提高精度而增加展开项数导致的计数造度变慢的问题,同时也节省了硬件资源。实验结果表明,基于该算法在DSP芯片中实现压张信号发生器所需的存储资源以及计算精度均优于其他方法。

关键调:泰物级数展开DSP正张信号存储单元复用

中图分类号:TP274 1引言

文献标识码:A

文章编号:1007-9416(2013)07-0163-02

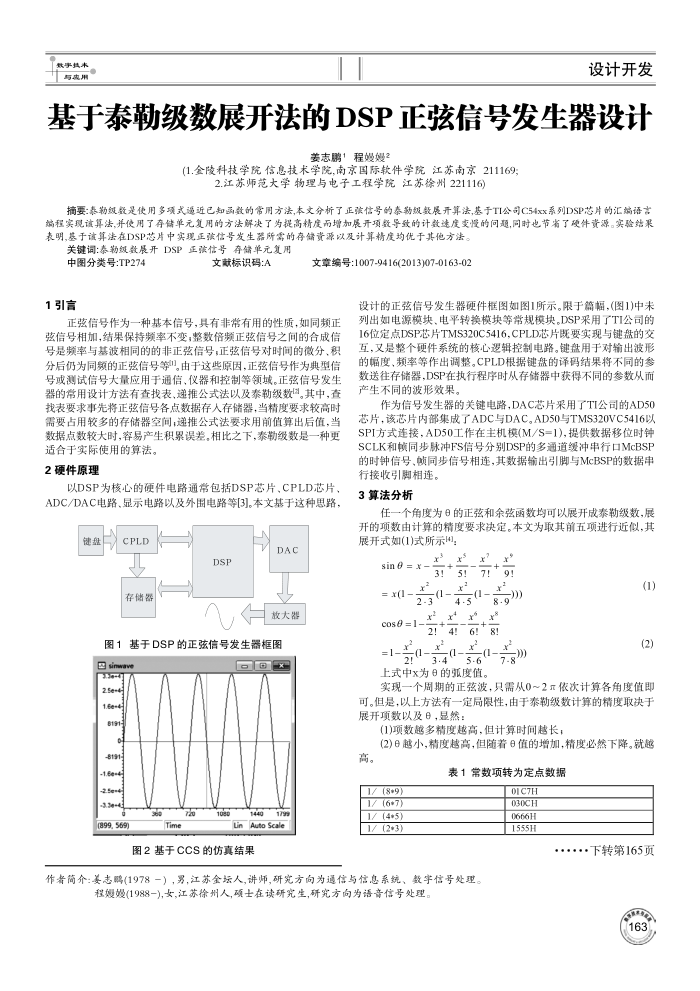

设计的正弦信号发生器硬件框图如图1所示。限于篇幅,(图1)中未

正兹信号作为一种基本信号,具有非常有用的性质,如同频正弦信号相加,结果保持频率不变;整数倍频正弦信号之间的合成信号是频率与基波相同的的非正信号,正弦信号对时闻的微分、积分后仍为同额的正弦信号等"。由于这些原因,正弦信号作为典型信号或测试信号大量应用于通信、仪器和控制等领域。正弦信号发生器的常用设计方法有查找表、递推公式法以及泰勒级数。其中,查找表要求事先将正弦信号各点数据存人存储器,当精度要求较高时需要占用较多的存储器空间,递推公式法要求用前值算出后值,当数据点数较大时,容易产生积累误差。相比之下,泰勒级数是一种更

适合于实际使用的算法。 2硬件原理

以DSP为核心的硬件电路通常包括DSP芯片、CPLD芯片, ADC/DAC电路、显示电路以及外围电路等[3]。本文基于这种思路,

键盘

CPLD 存储器

DSP

DAC 放大器

基于DSP的正弦信号发生器框图

图1 四sinwave

回回x

2.5e+4 1.6e-4 8191

-8191-1.6e 2.5e

-3.34

(899,569)

36

720

Time

1080

1440

1799

LinAuto Scale

图2基于CCS的仿真结果

列出如电源模块、电平转换模块等常规模块。DSP采用了TI公司的 16位定点DSP芯片TMS320C5416,CPLD芯片既要实现与键盘的交互,又是整个硬件系统的核心逻辑控制电路。键盘用于对输出波形的幅度、赖率等作出调整。CPLD根据键盘的译码结果将不同的参数送往存储器,DSP在执行程序时从存储器中获得不同的参数从而产生不同的波形效果。

作为信号发生器的关键电路,DAC芯片采用了TI公司的AD50 芯片,该芯片内部集成了ADC与DAC。AD50与TMS320VC5416以 SPI方式连接,AD50工作在主机模(M/S=1),提供数据移位时钟 SCLK和顿同步脉冲FS信号分别DSP的多通道缓冲串行口McBSP 的时钟信号、顺同步信号相连,其数据输出引脚与McBSP的数据审

行接收引脚相连。 3算法分析

任一个角度为的正弦和余弦函数均可以展开成泰勒级数,展开的项数由计算的精度要求决定。本文为取其前五项进行近似,其展开式如(1)式所示4):

sin o = x-

= x(1 -

x3

x5

x2

(-

2-3

cos6=1

4・5

x+

x

x

x 8.g

x

x

,9_-号-》

1-3

3.4

5・6

上式中x为的弧度值。

7-8

(1)(2)

实现一个周期的正弦波,只需从0~2π依次计算各角度值即可。但是,以上方法有一定局限性,由于泰勒级数计算的精度取决于展开项数以及6,显然:

(1)项数越多精度越高,但计算时间越长;

(2)e越小,精度越高,但随着日值的增加,精度必然下降。就越高。

表1常数项转为定点数据

1/ (8+9)(*9)/I 1/ (4+5) 1/ (2+3)

作者简介:姜志鹏(1978一),男,江苏金坛人,讲师,研完方向为通信与信息系统、数宇信号处理。

程嫂嫂(1988一),女,江苏徐州人,颈士在读研究生,研究方向为语章信号处理,

01C7H H300 0666H 1555H

.・.下转第165页

63