您当前的位置:首页>论文资料>高速CIC插值滤波器的位宽分析与优化

内容简介

2012年第09期,第45卷总第249期

2012年第09期,第45卷总第249期通信技术

Communications Technology

Vol.45,No.09,2012

No.249,Tota11y

高速CIC插值滤波器的位宽分析与优化

轰阳,戈华,赵鹏宇

(集宁师范学院物理系,内蒙古集宁012000)

【摘要】分析了级联积分-梳状(CIC,CascadedIntegratorComb)插值滤波器的位宽增长原因,重点研究了CIC插值滤波器非等值位宽的数据通路设计,在此基础上利用Matlab和XilinxSystemGenerato 开发工具搭建了电路的系统模型,最后通过现场可编程门阵列(FPGA,FieldProgrammableGateArray)完成电路的寄存器传输级(RTL,RegisterTransferLevel)验证,仿真结果表明电路设计具有很高的有效性和可行性,

【关键词】CIC插值滤波器;位宽;FPGA

【中图分类号】TN911.7

【文献标识码】A

【文章编号】1002-0802(2012)09-0143-03

AnalysisandOptimizationofHigh-Speed CICInterpolationFilter Width

NIEYang,GEHua,

ZHAOPeng-yu

(Dept of Physics, Jining Teachers College, Jining Inner Mongolia 012000, China )

【Abstract】 This paper analyzes the increase of CIC (Cascaded Integrator Comb) interpolation filter width, and focuses on the data path design of non equivalent width. Based on this and with Matlab and Xilinx System Generator development tools, the system model of the circuit is built up, and finally through FPGA (Field Programmable Gate Array) RTL (Register Transfer Level), the verification of the circuit is completed. And simulation indicates the effectiveness and feasibility of circuit design.

【Key words】 CIC interpolation filter: width: FPGA

0引言

随着现代无线通信中数据传输率的增加,在一个信号处理系统中常常需要不同的采样率处理信号以及不同采样率的信号之间相互转换。CIC插值滤波器的凭借其结构简单,以广泛应用于现代无线通信系统[1-2)。虽然,CIC插值滤波器的电路不使用乘法器,但是加法器的累加会导致数据通路的位宽增长。通过简单的位增长分析可以估计最大的位宽,若以最大位宽作为标准来设计数据通路,这样的设计并非必要,而目也浪费硬件资源。

就这一问题研究CIC插值滤波器的位宽,并利用收稿日期:2012-04-21。

*基金项目:2010年内蒙古自治区高等学校科学研究项目

(No. NJ10211)。

作者简介:聂阳(1980-),男,讲师主要研究方向为数

字信号处理的VLSI实现:戈华(1964-),男,教授,主要研究方向为数字信号处理:赵鹏宇(1981-),男,助教,主要研究方向为EDA 技术。

FPGA完成其电路设计及其验证。

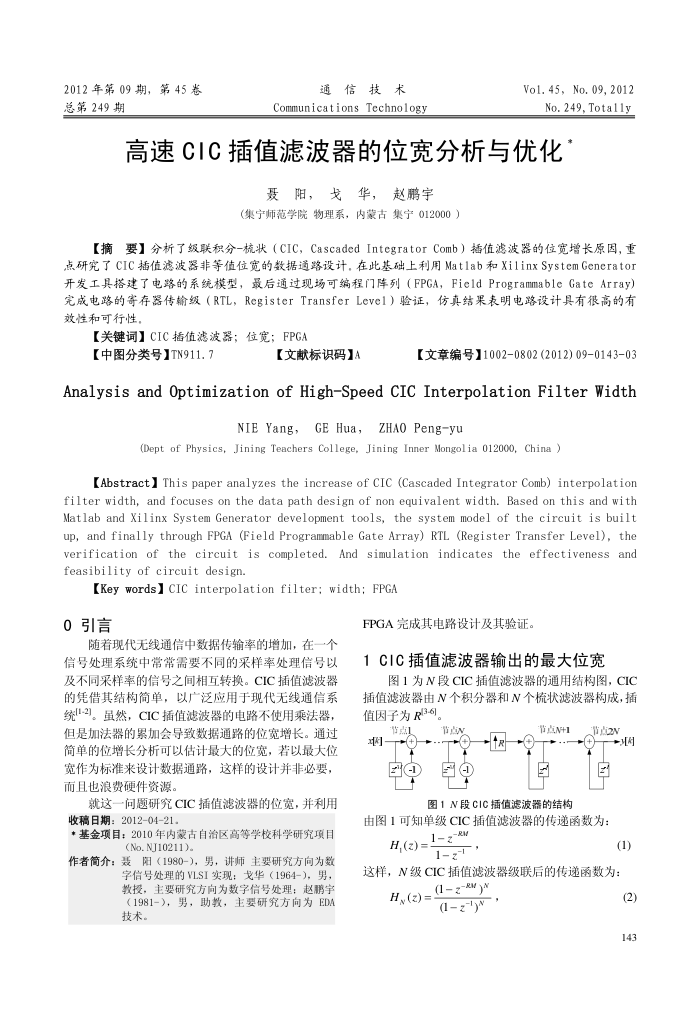

1CIC插值滤波器输出的最大位宽

图1为N段CIC插值滤波器的通用结构图,CIC 插值滤波器由N个积分器和N个梳状滤波器构成,插

值因子为R(3-6)。

点1 国

节点

节点N+1

节点2V

lyk+ 图

图1N段CIC插值滤波器的结构

由图1可知单级CIC插值滤波器的传递函数为:

1g-RV

H,(z)

1 3-1

(1)

这样,N级CIC插值滤波器级联后的传递函数为:

(1 RN )A

H(z):

(1 2")N

(2) 143

上一章:千兆以太网MAC中CRC算法的设计与实现

下一章:高速串行通道的信号完整性问题分析