内容简介

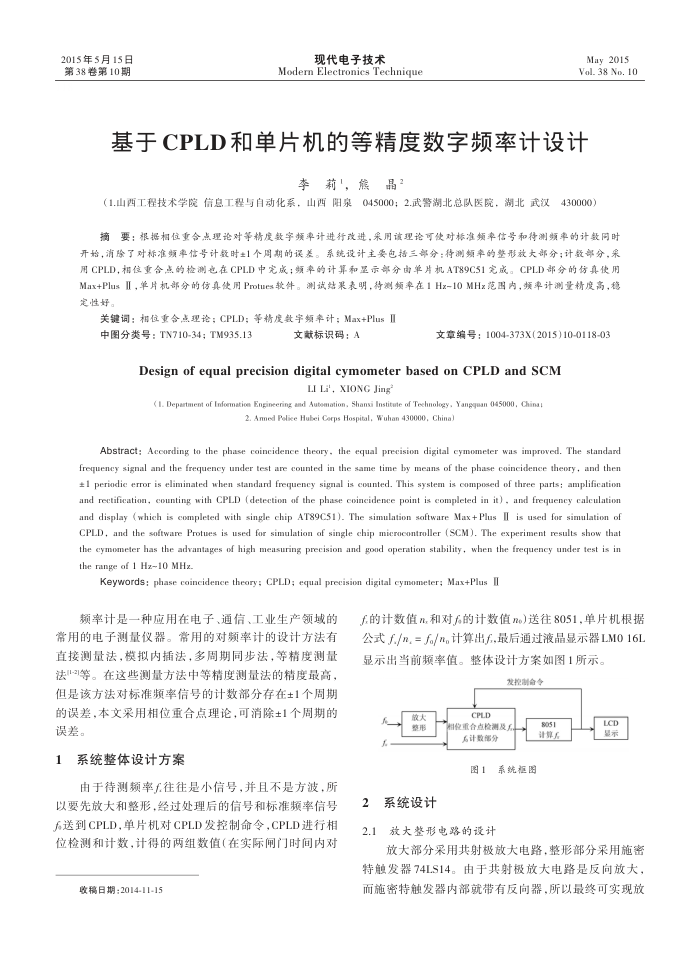

摘要:根据相位重合点理论对等精度数字频率计进行改进,采用该理论可使对标准频率信号和待测频率的计数同时开始,消除了对标准频率信号计数时±1 个周期的误差。系统设计主要包括三部分:待测频率的整形放大部分;计数部分,采用CPLD,相位重合点的检测也在 CPLD中完成;频率的计算和显示部分由单片机 AT89C51完成。CPLD 部分的仿真使用Max+Plus Ⅱ,单片机部分的仿真使用 Protues软件。测试结果表明,待测频率在1 Hz~10 MHz范围内,频率计测量精度高,稳定性好。