����ǰ��λ�ã���ҳ>��������>S ���ε�����ݱ�ƵƵ���ۺ������

S ���ε�����ݱ�ƵƵ���ۺ������

���ݼ��

��ƿ���

��ƿ���S���ε�����ݱ�ƵƵ���ۺ������

��������ϼ

(�Ϻ�����804���Ϻ�201109)

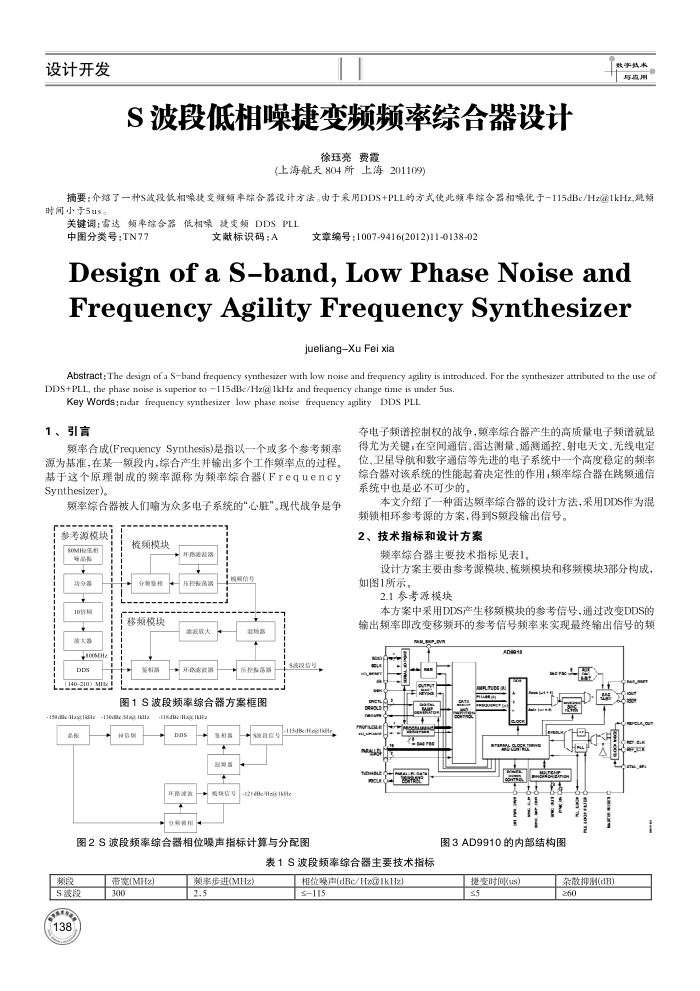

ժҪ��������һ��S���ε�����ݱ�ƵƵ���ۺ�����Ʒ��������ڲ���DDS+PLL�ķ�ʽʹ��Ƶ���ۺ�����������-115dBc/Hz@1kHz,��Ƶʱ��С��5u%��

�ؼ��������Ƶ���ۺ������������ƵDDSPLL ��ͼ����ţ�TN77

���ױ�ʶ�룺A

���±�ţ�1007-9416(2012)11-0138-02

Design of a S-band, Low Phase Noise and Freguency Agility Frequency Synthesizer

jueliangXu Fei xia

Abstract : The design of a Sband frequency synthesizer with low noise and frequency agility is introduced. For the synthesizer attributed to the use of DDS+PLL, the phase noise is superior to 115dBe/Hz@1kHz and frequency change time is under 5us.

Key Words;radar frequency synthesizer low phase noise frequency agility DDS PLL

1������

���ʺϳ�(FrequencySynthesis)��ָ��һ�������ο�Ƶ��ԴΪ������ijһ����ڣ��ۺϲ���������������Ƶ�ʵ�Ĺ��̡��������ԭ���Ƴɵ�Ƶ��Դ��ΪƵ���ۺ���(Frequency Synthesizer)��

�����ۺ�����������Ϊ�ڶ����ϵͳ�ġ����ࡱ���ִ�ս������

�ο�Դģ�飺 SOMHz��

9% o ������

OOMH DDs

��Ƶģ��

��Ҫ��Ƶģ��

������

Ͷ������

sa���ź�

ͼ1S����Ƶ���ۺ���������ͼ

Be/Hs1kH

��Ƶ��

ͼ2S����Ƶ���ۺ�����λ����ָ����������ͼ

�����Ƶ����Ȩ��ս���������ۺ��������ĸ���������Ƶ���Ե���Ϊ�ؼ����ڿ���ͨ�ţ��״������ͨ��ң�ء�������ġ����ߵ綨λ�����ǵ���������ͨ�ŵ��Ƚ��ĵ���ϵͳ��һ���߶��ȶ���Ƶ���ۺ����Ը�ϵͳ���������ž����Ե����ã�Ƶ���ۺ�������Ƶͨ��ϵͳ��Ҳ�DZز����ٵġ�

���Ľ�����һ���״�����ۺ�������Ʒ���������DDS��Ϊ��

Ƶ����ο�Դ�ķ������õ�SƵ������źš� 2������ָ�����Ʒ���

Ƶ���ۺ�����Ҫ����ָ�����1��

��Ʒ�����Ҫ���㿼Դģ�顢��Ƶģ�����Ƶģ�鲿�ֹ��ɣ���ͼ1��ʾ��

2.1�ο�Դģ��

�������в���DDS�����ƶ�ģ��IJο��źţ�ͨ���ı�DDS�����Ƶ�ʼ��ı���Ƶ���IJο��ź�Ƶ����ʵ����������źŵ�Ƶ

AD0018

ut

S

59

��1S����Ƶ���ۺ�����Ҫ����ָ��

Ƶ�� S����

38

����(MHz) 300

Ƶ�ʲ���(MHz) 2.5

�����(dBc/Hz@1kHz) ��115

AT

Ʒ

LIWBEN

ͼ3AD9910���ڲ��ṹͼ

�ݱ�ʱ��(us ��5

��ɢ����(dB) ��60

��һ�£�VoIP��NAT�MFW���������о�

��һ�£�����¼����ϵͳ�������ʵ��

�������

ƽ��ʽS���ε������Ŵ������

S ���ζ��������ֻ�������

QX/T 463-2018 S���ζ����������״�

QX/T 464-2018 S����˫��ƫ������������״�

Һѹ�������ۺ���������̨���������

�����źŵ�Ƶ�ʼ��Խݱ������ݱ�Ƶ��SAR�����ų���

GB/T 17215.324-2017 ����������豸����Ҫ���24���֡þ�ֹʽ����Ƶ�������ܱ���0.5S ����1S ���� 1 ��

GB/T 17215.324-2017 ����������豸 ����Ҫ�� ��24���֣���ֹʽ����Ƶ�������ܱ�(0.5S����1S����1��)