您当前的位置:首页>论文资料>高压VDMOS的设计

内容简介

,应用研究・

,应用研究・高压VDMOS的设计

都晓波

(西安卫光科技有限公司

陕西西安

710065)

数字技术与应用

摘要:本文通过VDMOS的电枣数来确定其结构奉数,通过击穿电压来确定外延层的厚度和电阻率,通过阅佳电压来确定据氧的厚度。由饱和电流的表达式可知元胞的最大通态电流。寻通电阻和去穿电压是两个相互手盾的参数,增加击穿电压和降低导通电阻对器件尺亨的要求是矛盾的。

版图

关键词:VDMOS

结构

中图分类号:TN386.1

设计霜标

文献标识码:A

文章编号:1007-9416(2010)08-0101-02

1引

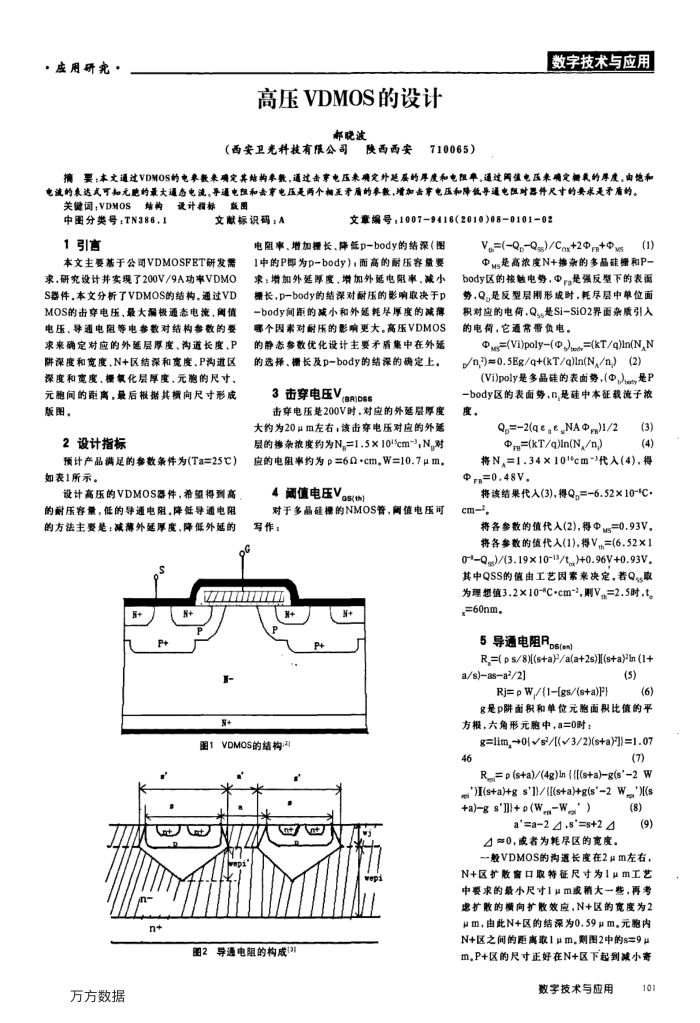

本文主要基于公司VDMOSFET研发需求,研究设计并实现了200V/9A功率VDMO S器件,本文分析了VDMOS的结构,通过VD MOS的击穿电压,最大漏极通态电流、阅值电压、导通电阻等电参数对结构参数的要求来确定对应的外延层厚度、沟道长度、P 阱深度和宽度,N+区结深和宽度、P沟道区深度和宽度,栅氧化层厚度,元胞的尺寸、元胞闻的距离,最后根据其横向尺寸形成版图。

2设计指标

预计产品满足的参数条件为(Ta=25C) 如表1所示。

设计高压的VDMOS器件,希望得到高的耐压容量,低的导通电阻,降低导通电阻的方法主要是:减幕外延厚度、降低外延的

+

P

+

电阻率、增加摄长、降低p-body的结深(图 1中的P即为p-body),而高的耐压容量要求:增加外延厚度,增加外延电阻率、减小摄长,p-body的结深对耐压的影响取决于p-body间距的减小和外延耗尽厚度的减幕个因素对耐压的影响更大。高压VDMOS 的静态参数优化设计主要矛盾集中在外延的选择、摄长及p-body的结深的确定上。

3击穿电压V(aA)D

击穿电压是200V时,对应的外延层厚度大约为20μm左右;该击穿电压对应的外延层的掺杂浓度约为N,=1.5×1015cm-3,N,对应的电阻率约为p=60+cm。W=10.7μm。

4阀值电压Vas(t)

对于多晶硅棚的NMOS管,阀值电压可写作:

图1VDMOS的结构

国国

vepi

n+

图2导通电阻的构成(3]

万方数据

V,=(Q,Qsg)/Cmx+2Φrg+Φμs

(1)

@us是高浓度N+杂的多晶硅摄和P body区的接触电势,中r是强反型下的表面务,Q,是反型层形成时,耗尽层中单位面积对应的电荷,Qs,是Si-SiO2界面杂质引人的电荷,它通常带负电。

@s=(Vi)poly(β )o,=(kT/q)ln(N,N/n,)=0.5Eg/q+(kT/q)In(N,/n,)(2)(Vi)poly是多品硅的表面势,(Φe是P-body区的表面势,n,是硅中本征载流子浓度。

Q,=2(qe,,NAΦ)1/2 中r=(kT/q)In(N,/n)

(3)(4)

将N=1.34×101cm-代入(4),得 Φr=0.48V.

将该结果代入(3),得Q,==6.52×10-C. cm-2

将各参数的值代入(2),得中ys=0.93V。将各参数的值代入(1),得V,三(6.52×1

0-*Q)/(3.19× 10-13/t.)+0.96V+0.93V, 其中QSS的值由工艺因素来决定,若Qss取为理想值3.2×10-*Ccm~3,则V,=2.5时,t。 =60nm。

5导通电阻Rps(an)

R,=( p s/8)[(s+a)/a(a+2s)[(s+a)2n (1+

a/s)as=a2/21

Rj= p W,/(1[gs/(s+a)P)

(5)

(6)

g是p阱面积和单位元胞面积比值的平方根,六角形元胞中,a二0时:

g=lim,→+0(Vs//[(v3/2)(s+a)])=1.07

46

(7)

R_,= p (s+a)/(4g)ln ([(s+a)g(s'2 W ei')(s+a)+g s'1/([(s+a)+g(s'2 w_'[(s

+a)g s'll+ p (W.W.a' )

a'=a2 4,s'=s+2 4 40,成者为耗尽区的宽度。

(8)(9)

一般VDMOS的沟道长度在2μm左右, N+区扩散窗口取特征尺寸为1μm工艺中要求的最小尺寸1μm或稍大一些,再考虑扩收的横向扩散效应,N+区的宽度为2 μm,由此N+区的结深为0.59μm。元胞内 N+区之间的距离取1μm,则图2中的s=9μ m。P+区的尺寸正好在N+区下起到减小膏

数字技术与应用

101

上一章:大型火电厂灰场的扬尘治理

下一章:C130活性粉末混凝土的配制技术